# Tru64 UNIX

# Assembly Language Programmer's Guide

Part Number: AA-PS31D-TE

March 1996

**Product Version:** Tru64 UNIX Version 4.0 or higher

This manual describes the assembly language supported by the Compaq Tru64 UNIX (formerly DIGITAL UNIX) Alpha compiler system, its syntax rules, and how to write some assembly programs.

#### © 1996 Compaq Computer Corporation

Portions of this document © MIPS Computer Systems, Inc., 1990.

COMPAQ, the Compaq logo, and the Digital logo are registered in the U.S. Patent and Trademark Office. Alpha, AlphaServer, NonStop, TruCluster, and Tru64 are trademarks of Compaq Computer Corporation.

Microsoft and Windows NT are registered trademarks of Microsoft Corporation. Intel, Pentium, and Intel Inside are registered trademarks of Intel Corporation. UNIX is a registered trademark and The Open Group is a trademark of The Open Group in the United States and other countries. Other product names mentioned herein may be the trademarks of their respective companies.

Possession, use, or copying of the software described in this publication is authorized only pursuant to a valid written license from Compaq Computer Corporation or an authorized sublicensor.

Compaq Computer Corporation shall not be liable for technical or editorial errors or omissions contained herein. The information in this document is subject to change without notice.

# **Contents**

# **About This Manual**

| 1 | Archit | Architecture-Based Considerations    |      |  |  |

|---|--------|--------------------------------------|------|--|--|

|   | 1.1    | Registers                            | 1–1  |  |  |

|   | 1.1.1  | Integer Registers                    | 1–1  |  |  |

|   | 1.1.2  | Floating-Point Registers             | 1–2  |  |  |

|   | 1.2    | Bit and Byte Ordering                | 1–2  |  |  |

|   | 1.3    | Addressing                           | 1–4  |  |  |

|   | 1.3.1  | Aligned Data Operations              | 1–4  |  |  |

|   | 1.3.2  | Unaligned Data Operations            | 1–4  |  |  |

|   | 1.4    | Exceptions                           | 1–5  |  |  |

|   | 1.4.1  | Main Processor Exceptions            | 1–5  |  |  |

|   | 1.4.2  | Floating-Point Processor Exceptions  | 1–5  |  |  |

| 2 | Lexica | al Conventions                       |      |  |  |

|   | 2.1    | Blank and Tab Characters             | 2–1  |  |  |

|   | 2.2    | Comments                             | 2–1  |  |  |

|   | 2.3    | Identifiers                          | 2–1  |  |  |

|   | 2.4    | Constants                            | 2–2  |  |  |

|   | 2.4.1  | Scalar Constants                     | 2–2  |  |  |

|   | 2.4.2  | Floating-Point Constants             | 2-2  |  |  |

|   | 2.4.3  | String Constants                     | 2–3  |  |  |

|   | 2.5    | Multiple Lines Per Physical Line     | 2–4  |  |  |

|   | 2.6    | Statements                           | 2-4  |  |  |

|   | 2.6.1  | Labels                               | 2-5  |  |  |

|   | 2.6.2  | Null Statements                      | 2–5  |  |  |

|   | 2.6.3  | Keyword Statements                   | 2–5  |  |  |

|   | 2.6.4  | Relocation Operands                  | 2–6  |  |  |

|   | 2.7    | Expressions                          | 2–8  |  |  |

|   | 2.7.1  | Expression Operators                 | 2–8  |  |  |

|   | 2.7.2  | Expression Operator Precedence Rules | 2–9  |  |  |

|   | 2.7.3  | Data Types                           | 2-10 |  |  |

|   | 2.7.4  | Type Propagation in Expressions      | 2–11 |  |  |

|   | 2.8    | Address Formats                      | 2–12 |  |  |

| 3 | Main I | nstruction Set                                      |      |

|---|--------|-----------------------------------------------------|------|

|   | 3.1    | Load and Store Instructions                         | 3–2  |

|   | 3.1.1  | Load Instruction Descriptions                       | 3–3  |

|   | 3.1.2  | Store Instruction Descriptions                      | 3–6  |

|   | 3.2    | Arithmetic Instructions                             | 3–8  |

|   | 3.3    | Logical and Shift Instructions                      | 3–14 |

|   | 3.4    | Relational Instructions                             | 3–16 |

|   | 3.5    | Move Instructions                                   | 3–17 |

|   | 3.6    | Control Instructions                                | 3–18 |

|   | 3.7    | Byte-Manipulation Instructions                      | 3-21 |

|   | 3.8    | Special-Purpose Instructions                        | 3–24 |

| 4 | Floati | ng-Point Instruction Set                            |      |

|   | 4.1    | Background Information on Floating-Point Operations | 4–2  |

|   | 4.1.1  | Floating-Point Data Types                           | 4–2  |

|   | 4.1.2  | Floating-Point Control Register                     | 4–3  |

|   | 4.1.3  | Floating-Point Exceptions                           | 4–4  |

|   | 4.1.4  | Floating-Point Rounding Modes                       | 4–5  |

|   | 4.1.5  | Floating-Point Instruction Qualifiers               | 4–7  |

|   | 4.2    | Floating-Point Load and Store Instructions          | 4–9  |

|   | 4.3    | Floating-Point Arithmetic Instructions              | 4-10 |

|   | 4.4    | Floating-Point Relational Instructions              | 4–13 |

|   | 4.5    | Floating-Point Move Instructions                    | 4–14 |

|   | 4.6    | Floating-Point Control Instructions                 | 4–15 |

|   | 4.7    | Floating-Point Special-Purpose Instructions         | 4–16 |

| 5 | Assen  | nbler Directives                                    |      |

| 6 | Progra | amming Considerations                               |      |

|   | 6.1    | Calling Conventions                                 | 6–1  |

|   | 6.2    | Program Model                                       | 6–2  |

|   | 6.3    | General Coding Concerns                             | 6–2  |

|   | 6.3.1  | Register Use                                        | 6–3  |

|   | 6.3.2  | Using Directives to Control Sections and Location   |      |

|   |        | Counters                                            | 6–4  |

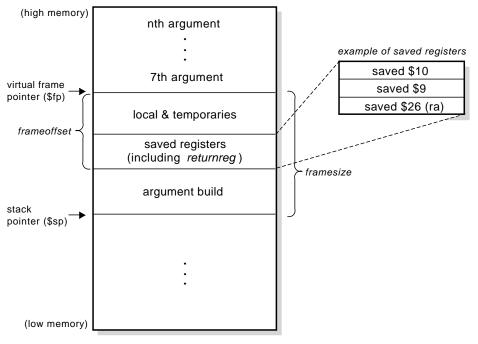

|   | 6.3.3  | The Stack Frame                                     | 6–5  |

|   | 6.3.4  | Examples                                            | 6–10 |

|   | 6.4    | Developing Code for Procedure Calls                 | 6–13 |

|   | 6.4.1  | Calling a High-Level Language Procedure             | 6–13 |

|   | 6.4.2   | Calling an Assembly-Language Procedure        | 6–15 |  |  |  |

|---|---------|-----------------------------------------------|------|--|--|--|

|   | 6.5     | Memory Allocation                             | 6–16 |  |  |  |

| 7 | Object  | Files                                         |      |  |  |  |

| 7 | Object  |                                               |      |  |  |  |

|   | 7.1     | Object File Overview                          | 7–1  |  |  |  |

|   | 7.2     | Object File Sections                          | 7–4  |  |  |  |

|   | 7.2.1   | File Header                                   | 7–4  |  |  |  |

|   | 7.2.2   | Optional Header                               | 7–5  |  |  |  |

|   | 7.2.3   | Section Headers                               | 7–6  |  |  |  |

|   | 7.2.4   | Section Data                                  | 7–10 |  |  |  |

|   | 7.2.5   | Section Relocation Information                | 7–13 |  |  |  |

|   | 7.2.5.1 | Relocation Table Entry                        | 7–13 |  |  |  |

|   | 7.2.5.2 | Assembler and Linker Processing of Relocation |      |  |  |  |

|   |         | Entries                                       | 7–16 |  |  |  |

|   | 7.3     | Object-File Formats (OMAGIC, NMAGIC, ZMAGIC)  | 7–21 |  |  |  |

|   | 7.3.1   | Impure Format (OMAGIC) Files                  | 7–22 |  |  |  |

|   | 7.3.2   | Shared Text (NMAGIC) Files                    | 7–23 |  |  |  |

|   | 7.3.3   | Demand Paged (ZMAGIC) Files                   | 7–24 |  |  |  |

|   | 7.3.4   | Ucode Objects                                 | 7–26 |  |  |  |

|   | 7.4     | Loading Object Files                          | 7–26 |  |  |  |

|   | 7.5     | Archive Files                                 | 7–27 |  |  |  |

|   | 7.6     | Linker Defined Symbols                        | 7–27 |  |  |  |

| 8 | Symbo   | Symbol Table                                  |      |  |  |  |

| • | •       |                                               | 0.4  |  |  |  |

|   | 8.1     | Symbol Table Overview                         | 8–1  |  |  |  |

|   | 8.2     | Format of Symbol Table Entries                | 8–8  |  |  |  |

|   | 8.2.1   | Symbolic Header                               | 8–8  |  |  |  |

|   | 8.2.2   | Line Number Table                             | 8–9  |  |  |  |

|   | 8.2.3   | Procedure Descriptor Table                    | 8–13 |  |  |  |

|   | 8.2.4   | Local Symbol Table                            | 8–14 |  |  |  |

|   | 8.2.4.1 | Symbol Type (st) Constants                    | 8–16 |  |  |  |

|   | 8.2.4.2 | Storage Class (sc) Constants                  | 8–17 |  |  |  |

|   | 8.2.5   | Auxiliary Symbol Table                        | 8–18 |  |  |  |

|   | 8.2.6   | File Descriptor Table                         | 8–22 |  |  |  |

|   | 8.2.7   | External Symbol Table                         | 8–22 |  |  |  |

| 9 | Progra  | m Loading and Dynamic Linking                 |      |  |  |  |

|   | 9.1     | Object File Considerations                    | 9–1  |  |  |  |

|   | 9.1.1   | Structures                                    | 9–1  |  |  |  |

|   | 9.1.2   | Base Addresses                                | 9–2  |  |  |  |

|   | J. 1.2  | Daso Huai ossos                               | J Z  |  |  |  |

|   | 9.1.3    | Segment Access Permissions                        | 9–2  |

|---|----------|---------------------------------------------------|------|

|   | 9.1.4    | Segment Contents                                  | 9–2  |

|   | 9.2 F    | Program Loading                                   | 9–3  |

|   | 9.3 I    | Dynamic Linking                                   | 9–4  |

|   | 9.3.1    | Dynamic Loader                                    | 9–4  |

|   | 9.3.2    | Dynamic Section (.dynamic)                        | 9–5  |

|   | 9.3.2.1  | Shared Object Dependencies                        | 9–13 |

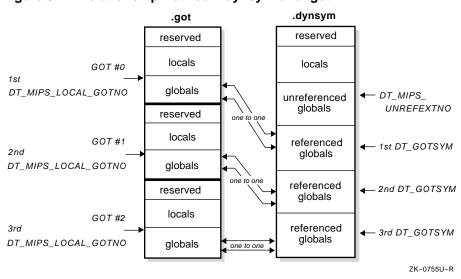

|   | 9.3.3    | Global Offset Table (.got)                        | 9–14 |

|   | 9.3.3.1  | Resolving Calls to Position-Independent Functions | 9–15 |

|   | 9.3.4    | Dynamic Symbol Section (.dynsym)                  | 9–17 |

|   | 9.3.5    | Dynamic Relocation Section (.rel.dyn)             | 9-20 |

|   | 9.3.6    | Msym Section (.msym)                              | 9–21 |

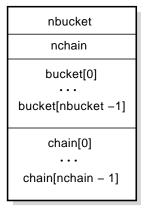

|   | 9.3.7    | Hash Table Section (.hash)                        | 9-22 |

|   | 9.3.8    | Dynamic String Section (.dynstr)                  | 9-23 |

|   | 9.3.9    | Initialization and Termination Functions          | 9-23 |

|   | 9.3.10   | Quickstart                                        | 9-23 |

|   | 9.3.10.1 | Shared Object List (.liblist)                     | 9–24 |

|   | 9.3.10.2 | Conflict Section (.conflict)                      | 9-25 |

|   | 9.3.10.3 | Ordering of Sections                              | 9–25 |

| A |          | ion Summaries                                     |      |

| В | 32-Bit C | considerations                                    |      |

|   |          | Canonical Form                                    | B-1  |

|   | B.2 I    | ongword Instructions                              | B-1  |

|   | B.3 G    | Quadword Instructions for Longword Operations     | B-2  |

|   | B.4 I    | ogical Shift Instructions                         | B-3  |

|   | B.5 C    | Conversions to Quadword                           | B-3  |

|   | B.6 C    | Conversions to Longword                           | B-3  |

| С | Basic M  | lachine Definition                                |      |

|   | C.1 I    | mplicit Register Use                              | C-1  |

|   |          | Addresses                                         | C-2  |

|   |          | mmediate Values                                   | C-3  |

|   |          | oad and Store Instructions                        | C-3  |

|   | _        | nteger Arithmetic Instructions                    | C-4  |

|   |          | Floating-Point Load Immediate Instructions        | C-4  |

|   |          |                                                   | C-4  |

|   | C.7 C    | One-to-One Instruction Mappings                   | U-4  |

| D.1<br>D.2 | Unprivileged PALcode Instructions                          | D–1<br>D–1 |

|------------|------------------------------------------------------------|------------|

| Index      |                                                            |            |

| Example    | s                                                          |            |

| 6–1        | Nonleaf Procedure                                          | 6–10       |

| 6–2        | Leaf Procedure Without Stack Space for Local Variables     | 6–11       |

| 6–3        | Leaf Procedure With Stack Space for Local Variables        | 6–11       |

| Figures    |                                                            |            |

| 1–1        | Byte Ordering                                              | 1–3        |

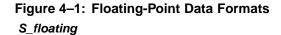

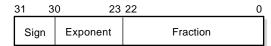

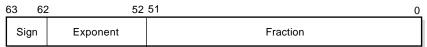

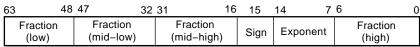

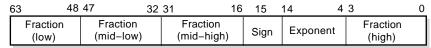

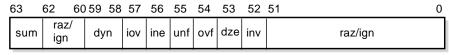

| 4–1        | Floating-Point Data Formats                                | 4–3        |

| 4–2        | Floating-Point Control Register                            | 4–4        |

| 6–1        | Sections and Location Counters for Nonshared Object Files  | 6–5        |

| 6–2        | Stack Organization                                         | 6–7        |

| 6–3        | Default Layout of Memory (User Program View)               | 6–17       |

| 7–1        | Object File Format                                         | 7–3        |

| 7–2        | Organization of Section Data                               | 7–11       |

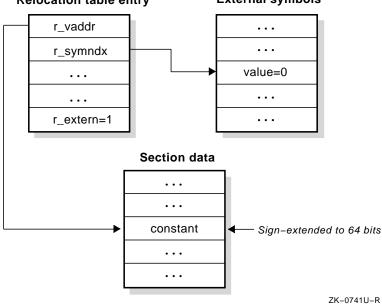

| 7–3        | Relocation Table Entry for Undefined External Symbols      | 7–17       |

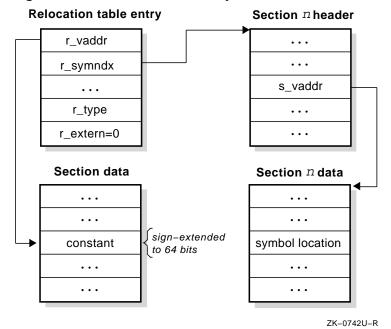

| 7–4        | Relocation Table Entry for a Local Relocation Entry        | 7–18       |

| 7–5        | Layout of OMAGIC Files in Virtual Memory                   | 7–22       |

| 7–6        | Layout of NMAGIC Files in Virtual Memory                   | 7–23       |

| 7–7        | Layout of ZMAGIC Files                                     | 7–25       |

| 8–1        | Symbol Table Overview                                      | 8–2        |

| 8–2        | Functional Overview of the Symbolic Header                 | 8–3        |

| 8–3        | Logical Relationship Between the File Descriptor Table and |            |

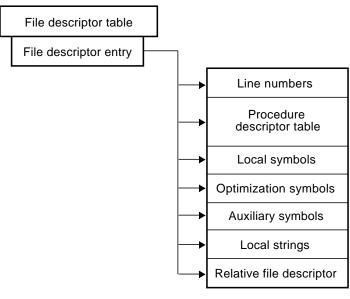

|            | Local Symbols                                              | 8–4        |

| 8–4        | Physical Relationship of a File Descriptor Entry to Other  |            |

|            | Tables                                                     | 8–6        |

| 8–5        | Logical Relationship Between the File Descriptor Table and |            |

|            | Other Tables                                               | 8–7        |

| 8–6        | Layout of Line Number Entries                              | 8–10       |

| 8–7        | Layout of Extended Line Number Entries                     | 8–11       |

| 9–1        | Text and Data Segments of Object Files                     | 9–3        |

| 9–2        | Relationship Between .dynsym and .got                      | 9–20       |

| 9–3        | Hash Table Section                                         | 9–22       |

**D** PALcode Instruction Summaries

#### **Tables** 2-1 Backslash Conventions ..... 2-3 2-2 2-8 Expression Operators ..... 2-3 Operator Precedence ..... 2-9 2 - 4Data Types ..... 2 - 102-5 Address Formats ..... 2-12 3-1 Load and Store Formats 3-2 3-2 Load Instruction Descriptions ..... 3 - 43-3 Store Instruction Descriptions ..... 3-6 3-4 Arithmetic Instruction Formats ..... 3-8 3-5 Arithmetic Instruction Descriptions ..... 3 - 103-6 Logical and Shift Instruction Formats ..... 3 - 143-7 Logical and Shift Instruction Descriptions ..... 3 - 153-8 Relational Instruction Formats ..... 3 - 173-9 Relational Instruction Descriptions ..... 3 - 173 - 10Move Instruction Formats ..... 3 - 183-11 Move Instruction Descriptions ..... 3 - 183 - 12Control Instruction Formats ..... 3-19 3-13 Control Instruction Descriptions ..... 3 - 193-14 Byte-Manipulation Instruction Formats ..... 3-21 3 - 15Byte-Manipulation Instruction Descriptions ..... 3 - 223 - 16Special-Purpose Instruction Formats ..... 3 - 243 - 173 - 25Special-Purpose Instruction Descriptions ..... 4–1 Qualifier Combinations for Floating-Point Instructions ...... 4-8 4-2 Load and Store Instruction Formats ..... 4-9 4-3 Load and Store Instruction Descriptions ..... 4-10 4-4 Arithmetic Instruction Formats ..... 4-10 4-5 Arithmetic Instruction Descriptions ..... 4-12 4-6 Relational Instruction Formats ..... 4-13 4-7 Relational Instruction Descriptions ..... 4-14 4-8 Move Instruction Formats ..... 4-14 4-9 Move Instruction Descriptions ..... 4-15 4-10 Control Instruction Formats ..... 4-15 4-11 Control Instruction Descriptions ..... 4-16 Special-Purpose Instruction Formats ..... 4-12 4-16 4-13 Control Register Instruction Descriptions ..... 4-16 5-1 Summary of Assembler Directives ..... 5-1 6-1 Integer Registers ..... 6-3 6–2 Floating-Point Registers ..... 6-4 6 - 36-9 Argument Locations .....

File Header Format

7-4

7–1

| 7–2  | File Header Magic Numbers                                | 7–4  |

|------|----------------------------------------------------------|------|

| 7–3  | File Header Flags                                        | 7–4  |

| 7–4  | Optional Header Definitions                              | 7–6  |

| 7–5  | Optional Header Magic Numbers                            | 7–6  |

| 7–6  | Section Header Format                                    | 7–7  |

| 7–7  | Section Header Constants for Section Names               | 7–7  |

| 7–8  | Format of s_flags Section Header Entry                   | 7–8  |

| 7–9  | Format of a Relocation Table Entry                       | 7–13 |

| 7–10 | Section Numbers for Local Relocation Entries             | 7–14 |

| 7–11 | Relocation Types                                         | 7–14 |

| 7–12 | Literal Usage Types                                      | 7–16 |

| 7–13 | Linker Defined Symbols                                   | 7–27 |

| 8–1  | Format of the Symbolic Header                            | 8–8  |

| 8–2  | Format of a Line Number Entry                            | 8–9  |

| 8–3  | Format of a Procedure Descriptor Table Entry             | 8–13 |

| 8–4  | Format of a Local Symbol Table Entry                     | 8–14 |

| 8–5  | Index and Value as a Function of Symbol Type and Storage |      |

|      | Class                                                    | 8–14 |

| 8–6  | Symbol Type (st) Constants                               | 8–16 |

| 8–7  | Storage Class Constants                                  | 8–17 |

| 8–8  | Auxiliary Symbol Table Entries                           | 8–19 |

| 8–9  | Format of a Type Information Record Entry                | 8–19 |

| 8–10 | Basic Type (bt) Constants                                | 8–20 |

| 8–11 | Type Qualifier (tq) Constants                            | 8–21 |

| 8–12 | Format of File Descriptor Entry                          | 8–22 |

| 8–13 | External Symbol Table Entries                            | 8-23 |

| 9–1  | Segment Access Permissions                               | 9–2  |

| 9–2  | Dynamic Array Tags (d_tag)                               | 9–6  |

| 9–3  | Processor-Specific Dynamic Array Tags (d_tag)            | 9–10 |

| A–1  | Main Instruction Set Summary                             | A-2  |

| A-2  | Floating-Point Instruction Set Summary                   | A-7  |

| A-3  | Rounding and Trapping Modes                              | A-10 |

| D-1  | Unprivileged PALcode Instructions                        | D-1  |

| D-2  | Privileged PALcode Instructions                          | D-2  |

# **About This Manual**

This book describes the assembly language supported by the Compaq Tru64 UNIX (formerly DIGITAL UNIX) compiler system, its syntax rules, and how to write some assembly programs. For information about assembling and linking a program written in assembly language, see the as(1) and ld(1) reference pages.

The assembler converts assembly language statements into machine code. In most assembly languages, each instruction corresponds to a single machine instruction; however, in the assembly language for the Tru64 UNIX compiler system, some instructions correspond to multiple machine instructions.

The assembler's primary purpose is to produce object modules from the assembly instructions generated by some high-level language compilers. As a result, the assembler lacks many functions that are normally present in assemblers designed to produce object modules from source programs coded in assembly language. It also includes some functions that are not found in such assemblers because of special requirements associated with the high-level language compilers.

### **Audience**

This manual assumes that you are an experienced assembly language programmer.

It is recommended that you use the assembler only when you need to perform programming tasks such as the following:

- Maximize the efficiency of a routine for example, a low-level I/O driver — in a way that might not be possible in C, Fortran-77, Pascal, or another high-level language.

- Access machine functions unavailable from high-level languages or satisfy special constraints such as restricted register usage.

- Change the operating system.

- · Change the compiler system.

# **New and Changed Features**

Many minor literary and technical changes have been made throughout this manual for the Version 4.0 release of Tru64 UNIX. The major technical changes to the manual are as follows:

- Chapter 2 Added information on support for relocation operands.

(See Section 2.6.4.)

- Chapter 3 Added information about the sextb and sextw instructions (see Section 3.2) and the amask and implyer instructions (see Section 3.8).

- Chapter 5 Added descriptions of the following directives: .lit4, .lit8, .arch, and tune.

# **Organization**

This manual is organized as follows:

- Chapter 1 Describes the format for the general registers, the special registers, and the floating-point registers. It also describes how addressing works and the exceptions you might encounter with assembly programs.

- *Chapter 2* Describes the lexical conventions that the assembler follows.

- Chapter 3 Describes the main processor's instruction set, including notation, load and store instructions, computational instructions, and jump and branch instructions.

- Chapter 4 Describes the floating-point instruction set.

- Chapter 5 Describes the assembler directives.

- Chapter 6 Describes calling conventions for all supported high-level languages. It also discusses memory allocation and register use.

- Chapter 7 Provides an overview of the components of the object file and describes the headers and sections of the object file.

- Chapter 8 Describes the purpose of the symbol table and the format of entries in the table. This chapter also lists the symbol table routines that are supplied.

- Chapter 9 Describes the object file structures that relate to program execution and dynamic linking, and also describes how the process image is created from these files.

- Appendix A Summarizes all assembler instructions.

- Appendix B Describes issues relating to processing 32-bit data.

- Appendix C Describes instructions that generate more than one machine instruction.

- Appendix D Describes the PALcode (privileged architecture library code) instructions required to support an Alpha system.

### **Related Documents**

The following manuals provide additional information on many of the topics addressed in this manual:

- Programmer's Guide

- The Alpha Architecture Reference Manual, 2nd Edition (Butterworth-Hinemann Press, ISBN:1-55558-145-5)

- · Calling Standard for Alpha Systems

#### Icons on Tru64 UNIX Printed Books

The printed version of the Tru64 UNIX documentation uses letter icons on the spines of the books to help specific audiences quickly find the books that meet their needs. (You can order the printed documentation from Compaq.) The following list describes this convention:

- G Books for general users

- S Books for system and network administrators

- P Books for programmers

- D Books for device driver writers

- R Books for reference page users

Some books in the documentation help meet the needs of several audiences. For example, the information in some system books is also used by programmers. Keep this in mind when searching for information on specific topics.

The *Documentation Overview* provides information on all of the books in the Tru64 UNIX documentation set.

### Reader's Comments

Compaq welcomes any comments and suggestions you have on this and other Tru64 UNIX manuals.

You can send your comments in the following ways:

- Fax: 603-884-0120 Attn: UBPG Publications, ZKO3-3/Y32

- Internet electronic mail: readers\_comment@zk3.dec.com

A Reader's Comment form is located on your system in the following location:

/usr/doc/readers\_comment.txt

Mail:

Compaq Computer Corporation UBPG Publications Manager ZKO3-3/Y32 110 Spit Brook Road Nashua, NH 03062-2698

A Reader's Comment form is located in the back of each printed manual. The form is postage paid if you mail it in the United States.

Please include the following information along with your comments:

- The full title of the book and the order number. (The order number is printed on the title page of this book and on its back cover.)

- The section numbers and page numbers of the information on which you are commenting.

- The version of Tru64 UNIX that you are using.

- If known, the type of processor that is running the Tru64 UNIX software.

The Tru64 UNIX Publications group cannot respond to system problems or technical support inquiries. Please address technical questions to your local system vendor or to the appropriate Compaq technical support office. Information provided with the software media explains how to send problem reports to Compaq.

### **Conventions**

| file   | Italic (slanted) type indicates variable values, placeholders, and function argument names.                                                                                                                                       |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [ ]    | In syntax definitions, brackets indicate items that are optional and braces indicate items that are required. Vertical bars separating items inside brackets or braces indicate that you choose one item from among those listed. |

| •••    | In syntax definitions, a horizontal ellipsis indicates that the preceding item can be repeated one or more times.                                                                                                                 |

| cat(1) | A cross-reference to a reference page includes the appropriate section number in parentheses. For example, cat(1) indicates that you can find information on the cat command in Section 1 of the reference pages.                 |

# **Architecture-Based Considerations**

This chapter describes programming considerations that are determined by the Alpha system architecture. It addresses the following topics:

- Registers (Section 1.1)

- Bit and byte ordering (Section 1.2)

- Addressing (Section 1.3)

- Exceptions (Section 1.4)

# 1.1 Registers

This section discusses the registers that are available on Alpha systems and describes how memory organization affects them. Refer to Section 6.3 for information on register use and linkage.

Alpha systems have the following types of registers:

- **Integer registers**

- Floating-point registers

You must use integer registers where the assembly instructions expect integer registers and floating-point registers where the assembly instructions expect floating-point registers. If you confuse the two, the assembler issues an error message.

The assembler reserves all register names (see Section 6.3.1). All register names start with a dollar sign (\$) and all alphabetic characters in register names are lowercase.

### 1.1.1 Integer Registers

Alpha systems have 32 integer registers, each of which is 64 bits wide. Integer registers are sometimes referred to as *general* registers in other system architectures.

The integer registers have the names \$0 to \$31.

By including the file regdef.h (use #include <alpha/regdef.h>) in your assembly language program, you can use the software names of all of the integer registers, except for \$28, \$29, and \$30. The operating system

and the assembler use the integer registers \$28, \$29, and \$30 for specific purposes.

| Note _ |  |

|--------|--|

|--------|--|

If you need to use the registers reserved for the operating system and the assembler, you must specify their alias names in your program, not their regular names. The alias names for \$28, \$29, and \$30 are \$at, \$gp, and \$sp, respectively. To prevent you from using these registers unknowingly and thereby producing potentially unexpected results, the assembler issues warning messages if you specify their regular names in your program.

The \$gp register (integer register \$29) is available as a general register on some non-Alpha compiler systems when the  $-G\ 0$  compilation option is specified. It is not available as a general register on Alpha systems under any circumstances.

Integer register \$31 always contains the value 0. All other integer registers can be used interchangeably, except for integer register \$30, which is assumed to be the stack pointer by certain PALcode. See Table 6–1 for a description of integer register assignments. See Appendix D and the *Alpha Architecture Handbook* for information on PALcode (Privileged Architecture Library code).

### 1.1.2 Floating-Point Registers

Alpha systems have 32 floating-point registers, each of which is 64 bits wide. Each register can hold one single-precision (32-bit) value or one double-precision (64-bit) value.

The floating-point registers have the names \$f0 to \$f31.

Floating-point register \$f31 always contains the value 0.0. All other floating-point registers can be used interchangeably. See Table 6–2 for a description of floating-point register assignments.

# 1.2 Bit and Byte Ordering

A system's byte-ordering scheme, or endian scheme, affects memory organization and defines the relationship between address and byte position of data in memory:

- Big-endian systems store the sign bit in the lowest address byte.

- Little-endian systems store the sign bit in the highest address byte.

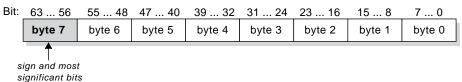

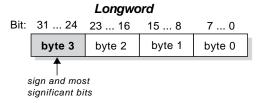

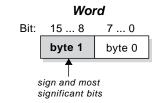

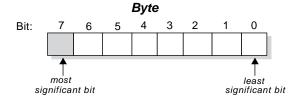

Figure 1-1: Byte Ordering

### Quadword

ZK-0732U-R

Alpha systems use the little-endian scheme. Byte-ordering is as follows:

- The bytes of a quadword are numbered from 7 to 0. Byte 7 holds the sign and most significant bits.

- The bytes of a longword are numbered from 3 to 0. Byte 3 holds the sign and most significant bits.

- The bytes of a word are numbered from 1 to 0. Byte 1 holds the sign and most significant bits.

The bits of each byte are numbered from 7 to 0, using the format shown in Figure 1–1. (Bit numbering is a software convention; no assembler instructions depend on it.)

# 1.3 Addressing

This section describes the byte-addressing schemes for load and store instructions. (Section 2.8 describes the formats in which you can specify addresses.)

### 1.3.1 Aligned Data Operations

All Alpha systems use the following byte-addressing scheme for aligned data:

- Access to words requires alignment on byte boundaries that are evenly divisible by two.

- Access to longwords requires alignment on byte boundaries that are evenly divisible by four.

- Access to quadwords requires alignment on byte boundaries that are evenly divisible by eight.

Any attempt to address a data item that does not have the proper alignment causes an alignment exception.

The following instructions load or store aligned data:

- Load quadword (1dg)

- Store quadword (stg)

- Load longword (1d1)

- Store longword (stl)

- Load word (ldw)

- Store word (stw)

- Load word unsigned (ldwu)

### 1.3.2 Unaligned Data Operations

The assembler's unaligned load and store instructions operate on arbitrary byte boundaries. They all generate multiple machine-code instructions. They do not raise alignment exceptions.

The following instructions load and store unaligned data:

- Unaligned load quadword (uldq)

- Unaligned store quadword (ustq)

- Unaligned load longword (uldl)

- Unaligned store longword (ust1)

- Unaligned load word (uldw)

- Unaligned store word (ustw)

- Unaligned load word unsigned (uldwu)

- Load byte (1db)

- Store byte (stb)

- Load byte unsigned (ldbu)

# 1.4 Exceptions

The Alpha system detects some exceptions directly, and other exceptions are signaled as a result of specific tests that are inserted by the assembler.

The following sections describe exceptions that you may encounter during the execution of assembly programs. Only those exceptions that occur most frequently are described.

### 1.4.1 Main Processor Exceptions

The following exceptions are the most common to the main processor:

- Address error exceptions occur when an address is invalid for the executing process or, in most instances, when a reference is made to a data item that is not properly aligned.

- Overflow exceptions occur when arithmetic operations compute signed values and the destination lacks the precision to store the result.

- Bus exceptions occur when an address is invalid for the executing process.

- Divide-by-zero exceptions occur when a divisor is zero.

### 1.4.2 Floating-Point Processor Exceptions

The following exceptions are the most common floating-point exceptions:

- Invalid operation exceptions include the following:

- Magnitude subtraction of infinities, for example, (+INF) (+INF).

- Multiplication of 0 by INF, with any signs.

- Division of 0 by 0 or INF; by INF, with any signs.

- Conversion of a binary floating-point number to an integer format, that is, only in those cases in which the conversion produces an overflow or an operand value of infinity or NaN. (The cvttq instruction converts floating-point numbers to integer formats.)

- Comparison of predicates that have unordered operands and involve Less Than or Less Than or Equal.

- Any operation on a signaling NaN. (See the introduction of Chapter 4 for a description of NaN symbols.)

- Divide-by-zero exceptions occur when a divisor is zero.

- Overflow exceptions occur when a rounded floating-point result exceeds the destination format's largest finite number.

- · Underflow exceptions occur when a result has lost accuracy and also when a nonzero result is between + -2  $^{\rm Emin}$  (plus or minus 2 to the minimum expressible exponent).

- Inexact exceptions occur if the infinitely precise result differs from the rounded result.

For additional information on floating-point exceptions, see Section 4.1.3.

# **Lexical Conventions**

This chapter describes lexical conventions associated with the following items:

- Blank and tab characters (Section 2.1)

- Comments (Section 2.2)

- Identifiers (Section 2.3)

- Constants (Section 2.4)

- Physical lines (Section 2.5)

- Statements (Section 2.6)

- Expressions (Section 2.7)

- Address formats (Section 2.8)

### 2.1 Blank and Tab Characters

You can use blank and tab characters anywhere between operators, identifiers, and constants. Adjacent identifiers or constants that are not otherwise separated must be separated by a blank or tab.

These characters can also be used within character constants; however, they are not allowed within operators and identifiers.

### 2.2 Comments

The number sign character (#) introduces a comment. Comments that start with a number sign extend through the end of the line on which they appear. You can also use C language notation (/\*...\*/) to delimit comments.

Do not start a comment with a number sign in column one; the assembler uses cpp (the C language preprocessor) to preprocess assembler code and cpp interprets number signs in the first column as preprocessor directives.

### 2.3 Identifiers

An identifier consists of a case-sensitive sequence of alphanumeric characters (A-Z, a-z, 0-9) and the following special characters:

• . (period)

- \_ (underscore)

- \$ (dollar sign)

Identifiers can be up to 31 characters long, and the first character cannot be numeric (0-9).

If an undefined identifier is referenced, the assembler assumes that the identifier is an external symbol. The assembler treats the identifier like a name specified by a .globl directive (see Chapter 5).

If the identifier is defined to the assembler and the identifier has not been specified as global, the assembler assumes that the identifier is a local symbol.

### 2.4 Constants

The assembler supports the following constants:

- Scalar constants

- Floating-point constants

- String constants

### 2.4.1 Scalar Constants

The assembler interprets all scalar constants as twos complement numbers. Scalar constants can be any of the digits 0123456789abcdefABCDEF.

Scalar constants can be either decimal, hexadecimal, or octal constants:

- Decimal constants consist of a sequence of decimal digits (0-9) without a leading zero.

- Hexadecimal constants consist of the characters 0x (or 0X) followed by a sequence of hexadecimal digits (0-9abcdefABCDEF).

- Octal constants consist of a leading zero followed by a sequence of octal digits (0-7).

### 2.4.2 Floating-Point Constants

Floating-point constants can appear only in floating-point directives (see Chapter 5) and in the floating-point load immediate instructions (see Section 4.2). Floating-point constants have the following format:

```

±d1[.d2][e|E±d3]

```

d1

is written as a decimal integer and denotes the integral part of the floating-point value.

is written as a decimal integer and denotes the fractional part of the floating-point value.

is written as a decimal integer and denotes a power of 10.

The "+" symbol (plus sign) is optional.

For example, the number .02173 can be represented as follows:

```

21.73E-3

```

The floating-point directives, such as .float and .double, may optionally use hexadecimal floating-point constants instead of decimal constants. A hexadecimal floating-point constant consists of the following elements:

```

[+|-] 0x[1|0].<hex-digits>h0x<hex-digits>

```

The assembler places the first set of hexadecimal digits (excluding the 0 or 1 preceding the decimal point) in the mantissa field of the floating-point format without attempting to normalize it. It stores the second set of hexadecimal digits in the exponent field without biasing them. If the mantissa appears to be denormalized, it checks to determine whether the exponent is appropriate. Hexadecimal floating-point constants are useful for generating IEEE special symbols and for writing hardware diagnostics.

For example, either of the following directives generates the single-precision number 1.0:

```

.float 1.0e+0

.float 0x1.0h0x7f

```

The assembler uses normal (nearest) rounding mode to convert floating-point constants.

# 2.4.3 String Constants

All characters except the newline character are allowed in string constants. String constants begin and end with double quotation marks (").

The assembler observes most of the backslash conventions used by the C language. Table 2–1 shows the assembler's backslash conventions.

Table 2-1: Backslash Conventions

| Convention | Meaning          |

|------------|------------------|

| \a         | Alert (0x07)     |

| <b>\b</b>  | Backspace (0x08) |

| \f         | Form feed (0x0c) |

Table 2–1: Backslash Conventions (cont.)

| Convention   | Meaning                                                                   |

|--------------|---------------------------------------------------------------------------|

| \n           | Newline (0x0a)                                                            |

| \r           | Carriage return (0x0d)                                                    |

| \t           | Horizontal tab (0x09)                                                     |

| \ <b>v</b>   | Vertical feed (0x0b)                                                      |

| \\           | Backslash (0x5c)                                                          |

| \"           | Quotation mark (0x22)                                                     |

| \'           | Single quote (0x27)                                                       |

| \nnn         | Character whose octal value is nnn (where n is 0-7)                       |

| <b>\X</b> nn | Character whose hexadecimal value is $nn$ (where $n$ is 0-9, a-f, or A-F) |

Deviations from C conventions are as follows:

- The assembler does not recognize "\?".

- The assembler does not recognize the prefix "L" (wide character constant).

- The assembler limits hexadecimal constants to two characters.

- The assembler allows the leading "x" character in a hexadecimal constants to be either uppercase or lowercase; that is, both \xnn and \Xnn are allowed.

For octal notation, the backslash conventions require three characters when the next character could be confused with the octal number.

For hexadecimal notation, the backslash conventions require two characters when the next character could be confused with the hexadecimal number. Insert a 0 (zero) as the first character of the single-character hexadecimal number when this condition occurs.

# 2.5 Multiple Lines Per Physical Line

You can include multiple statements on the same line by separating the statements with semicolons. Note, however, that the assembler does not recognize semicolons as separators when they follow comment symbols (# or /**\***).

### 2.6 Statements

The assembler supports the following types of statements:

- Null statements

- **Keyword statements**

Each keyword statement can include an optional label, an operation code (mnemonic or directive), and zero or more operands (with an optional comment following the last operand on the statement):

[ label]: opcode operand [; opcode operand; ...] [# comment]

Some keyword statements also support relocation operands (see Section 2.6.4).

### **2.6.1 Labels**

Labels can consist of label definitions or numeric values.

- A label definition consists of an identifier followed by a colon. (See Section 2.3 for the rules governing identifiers.) Label definitions assign the current value and type of the location counter to the name. An error results when the name is already defined.

- Label definitions always end with a colon. You can put a label definition on a line by itself.

- A numeric label is a single numeric value (1-255). Unlike label definitions, the value of a numeric label can be applied to any number of statements in a program. To reference a numeric label, put an f (forward) or a b (backward) immediately after the referencing digit in an instruction, for example, br 7f (which is a forward branch to numeric label 7). The reference directs the assembler to look for the nearest numeric label that corresponds to the specified number in the lexically forward or backward direction.

### 2.6.2 Null Statements

A null statement is an empty statement that the assembler ignores. Null statements can have label definitions. For example, the following line has three null statements in it:

```

label: ; ;

```

### 2.6.3 Keyword Statements

A keyword statement contains a predefined keyword. The syntax for the rest of the statement depends on the keyword. Keywords are either assembler instructions (mnemonics) or directives.

Assembler instructions in the main instruction set and the floating-point instruction set are described in Chapter 3 and Chapter 4, respectively. Assembler directives are described in Chapter 5.

### 2.6.4 Relocation Operands

Relocation operands are generally useful in only two situations:

- In application programs in which the programmer needs precise control over scheduling

- In source code written for compiler development

Some macro instructions (for example, 1dgp) require special coordination between the machine-code instructions and the relocation sequences given to the linker. By using the macro instructions, the assembler programmer relies on the assembler to generate the appropriate relocation sequences.

In some instances, the use of macro instructions may be undesirable. For example, a compiler that supports the generation of assembly language files may not want to defer instruction scheduling to the assembler. Such a compiler will want to schedule some or all of the machine-code instructions. To do this, the compiler must have a mechanism for emitting an object file's relocation sequences without using macro instructions. The mechanism for establishing these sequences is the relocation operand.

A relocation operand can be placed after the normal operand on an assembly language statement:

```

opcode operand relocation_operand

```

The syntax of the relocation operand is as follows:

! relocation\_type! sequence\_number

relocation type

Any one of the following relocation types can be specified:

```

literal

lituse base

lituse bytoff

lituse jsr

apdisp

gprelhigh

gprellow

```

The relocation types must be enclosed within a pair of exclamation points (!) and are not case sensitive. See Table 7–11 for descriptions of the different types of relocation operations.

sequence number

The sequence number is a numeric constant with a value range of 1 to 2147483647. The constant can be base 8, 10, or 16. Bases other than 10 require a prefix (see Section 2.4.1).

The following examples contain relocation operands in the source code:

• Example 1: Referencing multiple lituse base relocations

```

# Equivalent C statement:

# sym1 += sym2 (Both external)

# Assembly statements containing macro instructions:

$1, sym1

ldq

$2, sym2

addq $1, $2, $3

$3, sym1

stq

# Assembly statements containing machine-code instructions

# requiring relocation operandss:

ldq

$1, sym1($gp)!literal!1

ldq

$2, sym2($gp)!literal!2

ldq

$3, sym1($1)!lituse base!1

ldq

$4, sym2($1)!lituse base!2

addq $3, $4, $3

$3, sym1($1)!lituse base!1

```

The assembler stores the  ${\tt sym1}$  and  ${\tt sym2}$  address constants in the .lita section.

In this example, the code with relocation operands provides better performance than the other code because it saves on register usage and on the length of machine-code instruction sequences.

• Example 2: Referencing an ldgp sequence that is scheduled inside a lituse\_base relocation

```

# Assembly statements containing macro instructions:

beq $2, L

stq $31, sym

ldgp $gp, 0($27)

# Assembly statements containing machine-code instructions that

# require relocation operandss:

ldq $at, sym($gp)!literal!1

beq $2, L  # crosses basic block boundary

ldah $gp, 0($27)!gpdisp!2

stq $31, sym($at)!lituse_base!1

lda $gp, 0($gp)!gpdisp!2

```

In this example, the programmer has elected to schedule the load of the address of sym before the conditional branch.

• Example 3: A routine call

```

# Assembly statements containing macro instructions:

jsr sym1

ldqp $qp, 0($ra)

```

```

.extern sym1

.text

# Assembly statements containing machine-code instructions that

# require relocation operandss:

$27, sym1($gp)!literal!1

lda

$26, ($27), sym1!lituse_jsr!1

# as1 puts in an R_HINT for the jsr instruction

ldah $gp, 0($ra)!gpdisp!2

lda

$gp, 0($gp)!gpdisp!2

```

In this example, the code with relocation operands does not provide any significant gains over the other code. This example is only provided to show the different coding methods.

# 2.7 Expressions

An expression is a sequence of symbols that represents a value. Each expression and its result have data types. The assembler does arithmetic in twos complement integers with 64 bits of precision. Expressions follow precedence rules and consist of the following elements:

- **Operators**

- **Identifiers**

- Constants

You can also use a single character string in place of an integer within an expression. For example, the following two pairs of statements are equivalent:

```

.byte "a" ; .word "a"+0x19

.byte 0x61 ; .word 0x7a

```

### 2.7.1 Expression Operators

The assembler supports the operators shown in Table 2–2.

Table 2–2: Expression Operators

| Operator | Meaning        |

|----------|----------------|

| +        | Addition       |

| -        | Subtraction    |

| *        | Multiplication |

| /        | Division       |

| %        | Remainder      |

### Table 2–2: Expression Operators (cont.)

- << Shift left

- >> Shift right (sign is not extended)

- Bitwise EXCLUSIVE OR

- & Bitwise AND

- Bitwise OR

- Minus (unary)

- Identity (unary)

- Complement

### 2.7.2 Expression Operator Precedence Rules

For the order of operator evaluation within expressions, you can rely on the precedence rules or you can group expressions with parentheses. Unless parentheses enforce precedence, the assembler evaluates all operators of the same precedence strictly from left to right. Because parentheses also designate index registers, ambiguity can arise from parentheses in expressions. To resolve this ambiguity, put a unary + in front of parentheses in expressions.

The assembler has three precedence levels. The following table lists the precedence rules from lowest to highest:

Table 2 2: Operator Presedence

| Precedence                       | Operators                     |

|----------------------------------|-------------------------------|

| Least binding, lowest precedence | Binary +, -                   |

| •                                |                               |

|                                  | Binary *, /, %, <<, >>, ^, &, |

|                                  |                               |

| Most binding, highest precedence | Unary -, +, ~                 |

|                                  |                               |

|                                  | Note                          |

The assembler's precedence scheme differs from that of the C language.

# 2.7.3 Data Types

Each symbol you reference or define in an assembly program belongs to one of the type categories shown in Table 2-4.

Table 2-4: Data Types

| Туре      | Description                                                                                                                                                                                                                                                                                                                     |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| undefined | Any symbol that is referenced but not defined becomes global undefined. (Declaring such a symbol in a .globl directive merely makes its status clearer.)                                                                                                                                                                        |

| absolute  | A constant defined in an assignment (=) expression.                                                                                                                                                                                                                                                                             |

| text      | Any symbol defined while the .text directive is in effect belongs to the text section. The text section contains the program's instructions, which are not modifiable during execution.                                                                                                                                         |

| data      | Any symbol defined while the .data directive is in effect belongs to the data section. The data section contains memory that the linker can initialize to nonzero values before your program begins to execute.                                                                                                                 |

| sdata     | The type sdata is similar to the type data, except that defining a symbol while the .sdata ("small data") directive is in effect causes the linker to place it within the small data section. This increases the chance that the linker will be able to optimize memory references to the item by using gp-relative addressing. |

Table 2-4: Data Types (cont.)

| Туре             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rdata and rconst | Any symbol defined while the .rdata or .rconst directives are in effect belongs to this category. The only difference between the types rdata and rconst is that the former is allowed to have dynamic relocations and the latter is not. (The types rdata and rconst are also similar to the type data but, unlike data, cannot be modified during execution.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| bss and sbss     | Any symbol defined in a .comm or .lcomm directive belongs to these sections, except that a .data, .sdata, .rdata, or .rconst directive can override a .comm directive. The .bss and .sbss sections consist of memory that the kernel loader initializes to zero before your program begins to execute. If a symbol's size is less than the number of bytes specified by the -G compilation option (which defaults to eight), it belongs to .sbss section (small bss section), and the linker places it within the small data section. This increases the chance that the linker will be able to optimize memory references to the item by using gp-relative addressing.  Local symbols in the .bss or .sbss sections defined by .lcomm directives are allocated memory by the linker, and symbols defined by .comm directives are overlaid upon like-named symbols (in the fashion of Fortran COMMON blocks) by the linker. |

Symbols in the undefined category are always global; that is, they are visible to the linker and can be shared with other modules of your program. Symbols in the absolute, text, data, sdata, rdata, rconst, bss, and sbss type categories are local unless declared in a .globl directive.

### 2.7.4 Type Propagation in Expressions

For any expression, the result's type depends on the types of the operands and the operator. The following type propagation rules are used in expressions:

- If an operand is undefined, the result is undefined.

- If both operands are absolute, the result is absolute.

- If the operator is a plus sign (+) and the first operand refers to an undefined external symbol or a relocatable symbol in a .text section, .data section, or .bss section, the result has the first operand's type and the other operand must be absolute.

- If the operator is a minus sign (-) and the first operand refers to a relocatable symbol in a .text section, .data section, or .bss section, the type propagation rules can vary:

- The second operand can be absolute (if it was previously defined) and the result has the first operand's type.

- The second operand can have the same type as the first operand and the result is absolute.

- If the first operand is external undefined, the second operand must be absolute.

- The operators  $\star$ , /, \$, <<, >>, ~, ^, &, and | apply only to absolute symbols.

# 2.8 Address Formats

The assembler accepts addresses expressed in the formats described in Table 2-5.

Table 2-5: Address Formats

| Format                                 | Address Description                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (base-register)                        | Specifies an indexed address, which assumes a zero offset. The base register's contents specify the address.                                                                                                                                                                                                                                                                                                              |

| expression                             | Specifies an absolute address. The assembler generates the most locally efficient code for referencing the value at the specified address.                                                                                                                                                                                                                                                                                |

| expression(base-register)              | Specifies a based address. To get the address, the value of the expression is added to the contents of the base register. The assembler generates the most locally efficient code for referencing the value at the specified address.                                                                                                                                                                                     |

| relocatable-symbol                     | Specifies a relocatable address. The assembler generates the necessary instructions to address the item and generates relocation information for the linker.                                                                                                                                                                                                                                                              |

| $relocatable$ -symbol $\pm expression$ | Specifies a relocatable address. To get the address, the value of the expression, which has an absolute value, is added or subtracted from the relocatable symbol. The assembler generates the necessary instructions to address the item and generates relocation information for the linker. If the symbol name does not appear as a label anywhere in the assembly, the assembler assumes that the symbol is external. |

Table 2-5: Address Formats (cont.)

| Format                                               | Address Description                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| relocatable-symbol(index-register)                   | Specifies an indexed relocatable address. To get the address, the index register is added to the relocatable symbol's address. The assembler generates the necessary instructions to address the item and generates relocation information for the linker. If the symbol name does not appear as a label anywhere in the assembly, the assembler assumes that the symbol is external.                                                 |

| $relocatable-symbol \pm expression (index-register)$ | Specifies an indexed relocatable address. To get the address, the assembler adds or subtracts the relocatable symbol, the expression, and the contents of index register. The assembler generates the necessary instructions to address the item and generates relocation information for the link editor. If the symbol name does not appear as a label anywhere in the assembly, the assembler assumes that the symbol is external. |

# **Main Instruction Set**

The assembler's instruction set consists of a main instruction set and a floating-point instruction set. This chapter describes the main instruction set; Chapter 4 describes the floating-point instruction set. For details on the instruction set beyond the scope of this manual, refer to the *Alpha Architecture Reference Manual*.

The assembler's main instruction set contains the following classes of instructions:

- Load and store instructions (Section 3.1)

- Arithmetic instructions (Section 3.2)

- Logical and shift instructions (Section 3.3)

- Relational instructions (Section 3.4)

- Move instructions (Section 3.5)

- Control instructions (Section 3.6)

- Byte-manipulation instructions (Section 3.7)

- Special-purpose instructions (Section 3.8)

Tables in this chapter show the format of each instruction in the main instruction set. The tables list the instruction names and the forms of operands that can be used with each instruction. The specifiers used in the tables to identify operands have the following meanings:

| Operand Specifier | Description                                                                                                                                       |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| address           | A symbolic expression whose effective value is used as an address.                                                                                |

| b_reg             | Base register. An integer register containing a base address to which is added an offset (or displacement) value to produce an effective address. |

| d_reg             | Destination register. An integer register that receives a value as a result of an operation.                                                      |

| d_reg/s_reg       | One integer register that is used as both a destination register and a source register.                                                           |

| label             | A label that identifies a location in a program.                                                                                                  |

| Operand Specifier        | Description                                                                                                   |

|--------------------------|---------------------------------------------------------------------------------------------------------------|

| no_operands              | No operands are specified.                                                                                    |

| offset                   | An immediate value that is added to the contents of a base register to calculate an effective address.        |

| palcode                  | A value that determines the operation performed by a PALcode instruction.                                     |

| s_reg, s_reg1,<br>s_reg2 | Source registers whose contents are to be used in an operation.                                               |

| val_expr                 | An expression whose value is used as an absolute value.                                                       |

| val_immed                | An immediate value that is to be used in an operation.                                                        |

| jhint                    | An address operand that provides a hint of where a jmp or jsr instruction will transfer control.              |

| rhint                    | An immediate operand that provides software with a hint about how a ret or jsr_coroutine instruction is used. |

# 3.1 Load and Store Instructions

Load and store instructions load immediate values and move data between memory and general registers. This section describes the general-purpose load and store instructions supported by the assembler.

Table 3–1 lists the mnemonics and operands for instructions that perform load and store operations. The table is divided into groups of instructions. The operands specified within a particular group apply to all of the instructions contained in that group.

Table 3-1: Load and Store Formats

| Instruction                        | Mnemonic                        | Operands       |

|------------------------------------|---------------------------------|----------------|

| Load Address                       | lda <sup>a</sup>                | d_reg, address |

| Load Byte                          | ldb                             |                |

| Load Byte Unsigned                 | ldbu                            |                |

| Load Word                          | ldw                             |                |

| Load Word Unsigned                 | ldwu                            |                |

| Load Sign Extended Longword        | ${\tt ldl}^{\bf a}$             |                |

| Load Sign Extended Longword Locked | $ldl_l^a$                       |                |

| Load Quadword                      | ${\tt ldq}^{f a}$               |                |

| Load Quadword Locked               | ${\tt ldq\_l}^{\bm{a}}$         |                |

| Load Quadword Unaligned            | $_{\tt ldq\_u^{\color{red} b}}$ |                |

| Unaligned Load Word                | uldw                            |                |

Table 3-1: Load and Store Formats (cont.)

| Instruction                  | Mnemonic                    | Operands             |

|------------------------------|-----------------------------|----------------------|

| Unaligned Load Word Unsigned | uldwu                       |                      |

| Unaligned Load Word Unsigned | uldl                        |                      |

| Unaligned Load Longword      | uldq                        |                      |

| Load Address High            | ldah <sup>a</sup>           | d_reg, offset(b_reg) |

| Load Global Pointer          | ldgp                        |                      |

| Load Immediate Longword      | ldil                        | d_reg, val_expr      |

| Load Immediate Quadword      | ldiq                        |                      |

| Store Byte                   | stb                         | s_reg, address       |

| Store Word                   | stw                         |                      |

| Store Longword               | $\mathtt{stl}^{\mathbf{a}}$ |                      |

| Store Longword Conditional   | ${	t stl}_{	t c}^{	t a}$    |                      |

| Store Quadword               | $stq^{\mathbf{a}}$          |                      |

| Store Quadword Conditional   | stq_c <sup>a</sup>          |                      |

| Store Quadword Unaligned     | stq_u <sup>a</sup>          |                      |

| Unaligned Store Word         | ustw                        |                      |

| Unaligned Store Longword     | ustl                        |                      |

| Unaligned Store Quadword     | ustq                        |                      |

$<sup>\</sup>overline{a}$  In addition to the normal operands that can be specified with this instruction, relocation operands can also be specified (see Section 2.6.4).  $\overline{b}$  There's a b here but there is no text in the file for it. Put this here for a placeholder. Delete if it doesn't belong here

Section 3.1.1 describes the operations performed by load instructions and Section 3.1.2 describes the operations performed by store instructions.

### 3.1.1 Load Instruction Descriptions

Load instructions move values (addresses, values of expressions, or contents of memory locations) into registers. For all load instructions, the effective address is the 64-bit twos-complement sum of the contents of the index register and the sign-extended offset.

Instructions whose address operands contain symbolic labels imply an index register, which the assembler determines. Some assembler load instructions can produce multiple machine-code instructions (see Section C.4).

<sup>&</sup>lt;sup>D</sup> There's a b here but there is no text in the file for it. Put this here for a placeholder. Delete if it doesn't belong here or change to a.

| Note                                                                                                                              |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------|--|--|

| Load instructions can generate many code sequences for which<br>the linker must fix the address by resolving external data items. |  |  |

Table 3-2 describes the operations performed by load instructions.

Table 3–2: Load Instruction Descriptions

| Instruction                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Load Address (1da)                   | Loads the destination register with the effective address of the specified data item.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Load Byte (1db)                      | Loads the least significant byte of the destination register with the contents of the byte specified by the effective address. Because the loaded byte is a signed value, its sign bit is replicated to fill the other bytes in the destination register. (The assembler uses temporary registers AT and t9 for this instruction.)                                                                                                                                                                                                                                                                                          |

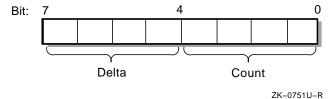

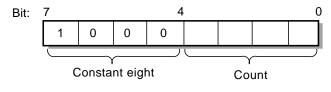

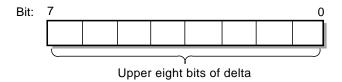

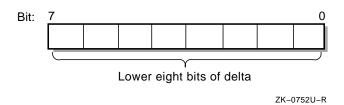

| Load Byte Unsigned (1dbu)            | Loads the least significant byte of the destination register with the contents of the byte specified by the effective address. Because the loaded byte is an unsigned value, the other bytes of the destination register are cleared to zeros. (The assembler uses temporary registers AT and t9 for this instruction — unless the setting of the .arch directive or the -arch flag on the cc or as command line causes the assembler to generate a single machine instruction in response to the ldbu command.)                                                                                                            |