# Tru64 UNIX

# Calling Standard for Alpha Systems

Part Number: AA-RH9MB-TE

August 2000

**Product Version:** Tru64 UNIX Version 5.1 or higher

This manual defines the requirements, mechanisms, and conventions used in the Tru64  $^{\text{TM}}$  UNIX interface that supports procedure calls for Tru64 UNIX on Alpha  $^{\text{TM}}$  systems.

#### © 2000 Compaq Computer Corporation

COMPAQ and the Compaq logo Registered in U.S. Patent and Trademark Office. Alpha and Tru64 are trademarks of Compaq Information Technologies Group, L.P.

Microsoft and Windows are trademarks of Microsoft Corporation. UNIX and The Open Group are trademarks of The Open Group. All Other product names mentioned herein may be trademarks or registered trademarks of their respective companies.

Confidential computer software. Valid license from Compaq required for possession, use, or copying. Consistent with FAR 12.211 and 12.212, Commercial Computer Software, Computer Software Documentation, and Technical Data for Commercial Items are licensed to the U.S. Government under vendor's standard commercial license.

Compaq shall not be liable for technical or editorial errors or omissions contained herein. The information in this document is provided "as is" without warranty of any kind and is subject to change without notice. The warranties for Compaq products are set forth in the express limited warranty statements accompanying such products. Nothing herein should be construed as constituting an additional warranty.

# **Contents**

## **About This Manual**

| 1 | Introdu | uction                        |      |

|---|---------|-------------------------------|------|

|   | 1.1     | Applicability                 | 1–2  |

|   | 1.2     | Architectural Level           | 1–2  |

|   | 1.3     | Goals                         | 1–3  |

|   | 1.4     | Requirements                  | 1–4  |

|   | 1.5     | Definitions                   | 1–4  |

| 2 | Tru64   | UNIX Concepts                 |      |

|   | 2.1     | Address Representation        | 2–1  |

|   | 2.2     | Procedure Representation      | 2–1  |

|   | 2.3     | Register Usage Conventions    | 2–2  |

|   | 2.3.1   | Integer Registers             | 2–2  |

|   | 2.3.2   | Floating-Point Registers      | 2–3  |

|   | 2.4     | Register Names                | 2-4  |

|   | 2.5     | Program Image Layout          | 2–4  |

| 3 | Flow C  | Control                       |      |

|   | 3.1     | Procedure Types               | 3–1  |

|   | 3.1.1   | Procedure Descriptor Overview | 3–1  |

|   | 3.1.2   | Stack Frame Procedure         | 3–4  |

|   | 3.1.2.1 | Stack Frame Format            | 3–4  |

|   | 3.1.2.2 | Register Save Area            | 3–7  |

|   | 3.1.3   | Register Frame Procedure      | 3–10 |

|   | 3.1.4   | Null Frame Procedure          | 3–11 |

|   | 3.2     | Transfer of Control           | 3–11 |

|   | 3.2.1   | Call Conventions              | 3–12 |

|   | 3.2.2   | Linkage                       | 3–14 |

|   | 3.2.3   | Link-Time Optimization        | 3–15 |

|   | 3.2.4   | Calling Computed Addresses    | 3–15 |

|   | 3.2.5   | Bound Procedure Values        | 3–16 |

|   | 3.2.6   | Entry and Exit Code Sequences | 3–17 |

|   | 3.2.6.1 | Entry Code Sequence           | 3–17 |

|   | 3.2.6.1.1<br>3.2.6.1.2 | Prologue Length                                   | 3–19<br>3–19 |

|---|------------------------|---------------------------------------------------|--------------|

|   | 3.2.6.1.3              | Entry Code Example for a Stack Frame              |              |

|   | 3.2.6.1.4              | Procedure Entry Code Example for a Register Frame | 3–19         |

|   |                        | Procedure                                         | 3-20         |

|   | 3.2.6.2                | Exit Code Sequence                                | 3–20         |

|   | 3.2.6.2.1              | Reserved Instruction Sequence for a Procedure     |              |

|   |                        | Exit                                              | 3–21         |

|   | 3.2.6.2.2              | Exit Code Sequence Steps                          | 3–23         |

|   | 3.2.6.2.3              | Exit Code Example for a Stack Frame Procedure .   | 3–24         |

|   | 3.2.6.2.4              | Exit Code Example for a Register Frame            |              |

|   |                        | Procedure                                         | 3–24         |

| 4 | Data Ma                | nipulation                                        |              |

|   | 4.1 D                  | Oata Passing                                      | 4–1          |

|   | 4.1.1                  | Argument Passing Mechanisms                       | 4–1          |

|   | 4.1.2                  | Normal Argument List Structure                    | 4–2          |

|   | 4.1.3                  | Homed Memory Argument List Structure              | 4–3          |

|   | 4.1.4                  | Argument Lists and High-Level Languages           | 4–5          |

|   | 4.1.5                  | Unused Bits in Passed Data                        | 4–5          |

|   | 4.1.6                  | Sending Data                                      | 4–7          |

|   | 4.1.6.1                | Sending Mechanism                                 | 4–8          |

|   | 4.1.6.2                | Order of Argument Evaluation                      | 4–9          |

|   | 4.1.7                  | Returning Data                                    | 4–9          |

|   | 4.1.7.1                | Function Value Return by Immediate Value          | 4-10         |

|   | 4.1.7.2                | Function Value Return by Reference                | 4-10         |

|   | 4.1.7.3                | Function Value Return by Descriptor               | 4–11         |

|   | 4.2 D                  | Oata Allocation                                   | 4–11         |

|   | 4.2.1                  | Data Alignment                                    | 4-12         |

|   | 4.2.2                  | Granularity of Memory                             | 4–13         |

|   | 4.2.3                  | Record Layout Conventions                         | 4–13         |

| 5 | Event Pi               | rocessing                                         |              |

|   | 5.1 E                  | Exception Handling                                | 5–1          |

|   | 5.1.1                  | Exception Handling Requirements                   | 5–2          |

|   | 5.1.2                  | Exception Handling Overview                       | 5–2          |

|   | 5.1.3                  | Kinds of Exceptions                               | 5–3          |

|   | 5.1.3.1                | General Exceptions                                | 5–4          |

|   | 5.1.3.2                | Unwind Exceptions                                 | 5–4          |

|   | 5.1.3.3                | Signal Exceptions                                 | 5–5          |

|   |                        |                                                   |              |

| 5.1.4    | Status Values and Exception Codes                | 5–5  |

|----------|--------------------------------------------------|------|

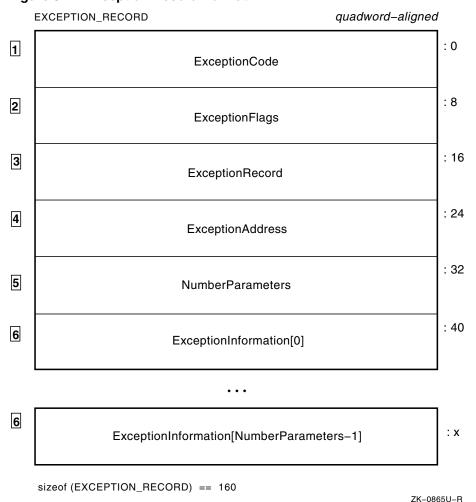

| 5.1.5    | Exception Records                                | 5–6  |

| 5.1.5.1  | Exception Records for General Exceptions         | 5–9  |

| 5.1.5.2  | Exception Records for Unwind Exceptions          | 5–9  |

| 5.1.5.3  | Exception Records for Signal Exceptions          | 5–9  |

| 5.1.6    | Frame-Based Exception Handlers                   | 5–10 |

| 5.1.7    | Establishing Handlers                            | 5–10 |

| 5.1.8    | Raising Exceptions                               | 5–11 |

| 5.1.8.1  | Raising General Exceptions                       | 5–12 |

| 5.1.8.2  | Raising General Exceptions Using gentrap         | 5–12 |

| 5.1.8.3  | Raising Unwind Exceptions                        | 5–14 |

| 5.1.8.4  | Raising Signal Exceptions                        | 5–14 |

| 5.1.9    | Search for and Invocation of Exception Handlers  | 5–14 |

| 5.1.9.1  | Invocation Order for Exception Handlers          | 5–14 |

| 5.1.9.2  | Handler Invocation and Arguments                 | 5–17 |

| 5.1.10   | Modification of Exception Records and Context by |      |

|          | Handlers                                         | 5–18 |

| 5.1.11   | Handler Completion and Return Value              | 5–19 |

| 5.1.11.1 | Completion by Reraising the Exception            | 5–20 |

| 5.1.11.2 | Completion by Continuing Thread Execution        | 5–20 |

| 5.1.11.3 | Completion During Unwinding                      | 5–20 |

| 5.1.11.4 | Completion from Signal Exceptions                | 5–20 |

| 5.1.12   | Other Considerations in Handling Exceptions      | 5–20 |

| 5.1.12.1 | Exception Synchronization                        | 5–21 |

| 5.1.12.2 | Continuation from Exceptions                     | 5-22 |

| 5.1.13   | Exception and Signal Handling Coexistence        | 5-22 |

| 5.2 U    | nwinding                                         | 5-24 |

| 5.2.1    | Overview of Unwinding                            | 5-24 |

| 5.2.2    | Types of Unwind Operations                       | 5–25 |

| 5.2.2.1  | General Unwind                                   | 5–25 |

| 5.2.2.2  | Exit Unwind                                      | 5–25 |

| 5.2.3    | Types of Unwind Invocations                      | 5–26 |

| 5.2.3.1  | Unwind Operations with No Active Exception       | 5–26 |

| 5.2.3.2  | Unwind Operations During an Active Exception     | 5–26 |

| 5.2.4    | Unwind Initiation                                | 5–27 |

| 5.2.5    | Unwinding from an Inserted Code Range            | 5–28 |

| 5.2.6    | Multiply Active Unwind Operations                | 5–28 |

| 5.2.6.1  | Nested Unwind                                    | 5–29 |

| 5.2.6.2  | Colliding Unwind                                 | 5–29 |

| 5.2.7    | Unwind Completion                                | 5–29 |

| 5.2.8    | Unwinding Coexistence with setjmp and longjmp    | 5–30 |

| 6   | Stack                                                                     | Limits in Multithreaded Execution Environments                                                                                                                                                                                                                                                                                                              |                                                                             |

|-----|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

|     | 6.1<br>6.1.1<br>6.1.2<br>6.1.2.1<br>6.1.2.2<br>6.1.3<br>6.2               | Stack Limit Checking Stack Region Definitions Methods for Stack Limit Checking Implicit Stack Limit Checking Explicit Stack Limit Checking Stack Reserve Region Checking Stack Overflow Handling                                                                                                                                                            | 6-1<br>6-2<br>6-2<br>6-3<br>6-4<br>6-5<br>6-5                               |

| 7   | Proced                                                                    | lure Invocations and Call Chains                                                                                                                                                                                                                                                                                                                            |                                                                             |

|     | 7.1<br>7.2<br>7.3                                                         | Referencing a Procedure Invocation                                                                                                                                                                                                                                                                                                                          | 7–1<br>7–2<br>7–2                                                           |

| 8   | Proced                                                                    | lure Descriptors                                                                                                                                                                                                                                                                                                                                            |                                                                             |

|     | 8.1<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.3.1<br>8.1.3.2<br>8.2<br>8.3        | Procedure Descriptor Representation Code Range Descriptors Run-Time Procedure Descriptors Examples Multiple Entry Point Example Instrumented Code Example Procedure Descriptor Access Routines Run-Time Generated Code                                                                                                                                      | 8–1<br>8–3<br>8–5<br>8–12<br>8–12<br>8–14<br>8–16<br>8–18                   |

| Inc | lex                                                                       |                                                                                                                                                                                                                                                                                                                                                             |                                                                             |

| Fig | jures                                                                     |                                                                                                                                                                                                                                                                                                                                                             |                                                                             |

|     | 3-1<br>3-2<br>3-3<br>3-4<br>4-1<br>5-1<br>5-2<br>5-3<br>8-1<br>8-2<br>8-3 | Fixed Size Stack Frame Format  Variable Size Stack Frame Format  Register Save Area Layout  Register Save Area Example  In-Memory Homed Argument List Structure  Status Value Representation  Exception Record Format  Procedure Invocation Chain  Code Range Descriptor  Long Form Run-Time Procedure Descriptor  Short Form Run-Time Procedure Descriptor | 3–5<br>3–6<br>3–9<br>3–10<br>4–4<br>5–5<br>5–7<br>5–16<br>8–4<br>8–7<br>8–8 |

# **Tables**

| 2–1 | Cananal Durmaga Integan Pagistana | 2-2  |

|-----|-----------------------------------|------|

|     | General-Purpose Integer Registers |      |

| 2–2 | Floating-Point Registers          | 2–3  |

| 3–1 | Procedure Properties Summary      | 3–2  |

| 4–1 | Argument Item Locations           | 4–2  |

| 4–2 | Unused Bits in Passed Data        | 4–6  |

| 4–3 | Data Alignment Addresses          | 4–12 |

| 5–1 | gentran EXPT CODE Values          | 5-13 |

# **About This Manual**

This manual defines the requirements, mechanisms, and conventions that are used in the UNIX interface that supports procedure calls for  $\mathsf{Tru64^{\mathsf{TM}}}$  UNIX for  $\mathsf{Alpha^{\mathsf{TM}}}$  systems. The standard defines the data structures, constants, algorithms, conventions, methods, and functional interfaces that enable a native user-mode procedure to operate correctly in a multilanguage and multithreaded environment on Tru64 UNIX systems operating on Alpha hardware.

## **Audience**

Although this manual primarily defines requirements for compiler and debugger writers, the information applies to procedure calling for all programmers at all levels of programming.

# **New and Changed Features**

Changes or additions to information on the following topics have been made to this manual for the Version 5.1 release of Tru64 UNIX:

- Chapter 4:

- Passing extended-precision complex values by reference Section 4.1.2

- Passing single- and double-precision complex values as two real values in two argument items — Section 4.1.6.1

- Quadword alignment of global variables Section 4.2.1

- Granularity requirements of byte and word instructions Section 4.2.2

- Chapter 5:

Unwinding from an inserted code range — Section 5.2.5

- Chapter 8:

- New fields in code range descriptors and procedure descriptors to define the context of any given instruction in a procedure — Section 8.1.1 and Section 8.1.2

- Examples showing use of code range descriptors and procedure descriptors — Section 8.1.3

# **Organization**

This document includes eight chapters:

| Chapter 1 | Introduces the standard and provides definitions of terms used in the standard.           |

|-----------|-------------------------------------------------------------------------------------------|

| Chapter 2 | Describes the fundamental concepts of the Tru64 UNIX calling standard for Alpha systems.  |

| Chapter 3 | Describes the aspects of the standard that deal with flow control.                        |

| Chapter 4 | Discusses the passing and storage of data.                                                |

| Chapter 5 | Discusses how the standard relates to events outside the normal program flow.             |

| Chapter 6 | Discusses stack limit checking in multithreaded execution environments.                   |

| Chapter 7 | Describes the mechanisms for functions that are needed to support procedure call tracing. |

| Chapter 8 | Discusses procedure descriptors.                                                          |

## **Related Documents**

This Tru64 UNIX calling standard is a component of the larger Alpha Software Architecture and depends on standards and conventions not described in this document. These standards include:

- Object language (including link-time optimizations) and object file format

- Status values and message definition, formatting, and reporting

- Heap memory management and dynamic string management

- Multithread architecture

- Names and naming conventions

The following documents contain information related to this standard and the standards mentioned in the previous list:

- Alpha Architecture Reference Manual, 2nd Edition (Butterworth-Hinemann Press, ISBN:1-55558-145-5)

- Programmer's Guide

- Assembly Language Programmer's Guide

- Guide to DECthreads

- Object File / Symbol Table Format Specification (This manual is available in HTML and PDF formats on the Tru64 UNIX Documentation CD-ROM, V5.0 and higher; it is not available in hardcopy or in PostScript format.)

- Compaq Portable Mathematics Library

- POSIX Conformance Document

- Information Technology Portable Operating System Interface (POSIX)

Part 1: System Application Program Interface (API) [C Language]

ISO/IEC 9945-1: 1990

- American National Standard for Information Systems Programming Language C – ANSI X3.159-1989 and its international equivalent, ISO/IEC 9899

#### Icons on Tru64 UNIX Printed Manuals

The printed version of the Tru64 UNIX documentation uses letter icons on the spines of the manuals to help specific audiences quickly find the manuals that meet their needs. (You can order the printed documentation from Compaq.) The following list describes this convention:

- G Manuals for general users

- S Manuals for system and network administrators

- P Manuals for programmers

- R Manuals for reference page users

Some manuals in the documentation help meet the needs of several audiences. For example, the information in some system manuals is also used by programmers. Keep this in mind when searching for information on specific topics.

The *Documentation Overview* provides information on all of the manuals in the Tru64 UNIX documentation set.

## **Reader's Comments**

Compaq welcomes any comments and suggestions you have on this and other Tru64 UNIX manuals.

You can send your comments in the following ways:

- Fax: 603-884-0120 Attn: UBPG Publications, ZKO3-3/Y32

- Internet electronic mail: readers comment@zk3.dec.com

A Reader's Comment form is located on your system in the following location:

```

/usr/doc/readers comment.txt

```

Please include the following information along with your comments:

- The full title of the manual and the order number. (The order number appears on the title page of printed and PDF versions of a manual.)

- The section numbers and page numbers of the information on which you are commenting.

- The version of Tru64 UNIX that you are using.

- If known, the type of processor that is running the Tru64 UNIX software.

The Tru64 UNIX Publications group cannot respond to system problems or technical support inquiries. Please address technical questions to your local system vendor or to the appropriate Compaq technical support office. Information provided with the software media explains how to send problem reports to Compaq.

## **Conventions**

This document uses the following typographical and symbol conventions:

| %      |                                                                                                                                                                                                                                   |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| \$     | A percent sign represents the C shell system prompt. A dollar sign represents the system prompt for the Bourne, Korn, and POSIX shells.                                                                                           |

| % cat  | Boldface type in interactive examples indicates typed user input.                                                                                                                                                                 |

| file   | Italic (slanted) type indicates variable values, placeholders, and function argument names.                                                                                                                                       |

| []]    |                                                                                                                                                                                                                                   |

| { }    | In syntax definitions, brackets indicate items that are optional and braces indicate items that are required. Vertical bars separating items inside brackets or braces indicate that you choose one item from among those listed. |

| cat(1) | A cross-reference to a reference page includes<br>the appropriate section number in parentheses.<br>For example, cat(1) indicates that you can find<br>information on the cat command in Section 1 of<br>the reference pages.     |

The following presentation conventions apply to this standard:

• Constants, data structures, and functional interfaces

Constants are represented symbolically with their values given at the point of definition in the standard. Data structures are defined in terms of the physical memory format of each structure. Functional interface syntax is presented in abstract form. Concrete language bindings for each constant, data structure, and functional interface are provided in system definition files external to the standard.

#### Algorithms

Algorithms are presented as a series of steps in standard American English.

#### Numbering

All numbers are represented as decimal values unless otherwise indicated. Nondecimal numbers are represented with the base name in parentheses following the number, for example, 1B (hex).

## · Memory and register layouts

Figures that represent memory or register layouts follow the convention that increasing addresses run from top to bottom and right to left. The most significant bits are on the left; the least significant bits are on the right.

## Code examples

All code examples are supplied to clarify the concept under discussion. These examples do not necessarily reflect the optimized or properly scheduled code sequences that a compiler would generate. The assembly language syntax follows the conventions used in the *Assembly Language Programmer's Guide*.

#### Record fields

Record fields are referred to by using the name of the record or subrecord followed by a dot (.) and then the field name:

record-name.subrecord-name.field

# Introduction

This manual defines the requirements, mechanisms, and conventions used in the Tru64 UNIX interface that supports procedure calls for Tru64 UNIX for Alpha systems. The standard defines the data structures, constants, algorithms, conventions, methods, and functional interfaces that enable a native user-mode procedure to operate correctly in a multilanguage and multithreaded environment on Tru64 UNIX systems operating on Alpha hardware.

This standard also defines properties of the run-time environment that must apply at various points during program execution. These properties vary in scope and applicability. Some properties apply to all points throughout the execution of standard-conforming user-mode code and must, therefore, be held constant at all times. Such properties include those defined for the stack pointer and various properties of the call-chain navigation mechanism. Other properties apply only at certain points; for example, call conventions that apply only at the point of transfer of control to another procedure.

Furthermore, some properties are optional, depending on circumstances. For example, compilers are not obligated to follow the argument list conventions when a procedure and all of its callers are in the same module, have been analyzed by an interprocedural analyzer, or have private interfaces such as language-support routines.

|       |       | Note _ | <br>     |  |

|-------|-------|--------|----------|--|

| mı .c | 41. : | 11     | <br>• "- |  |

The specifications in this standard are presented in an "as if" manner; that is, all conformant code must behave as if the specifications have been met. This standard is designed so that additional link-time information can be utilized to optimize or even remove instructions in critical code paths and, as such, achieve higher performance levels.

In many cases, significant performance gains can be realized by selective use of nonstandard calls when the safety of such calls is known. Compiler writers are encouraged to make full use of such optimizations, but should make sure that procedures outside the compilation unit can proceed as if the standard were met.

The conventions specified in this standard are intended to exploit fully the architectural and performance advantages of the Alpha hardware. Some of these conventions are visible to the high-level language programmer and, therefore, might require source changes in high-level language programs when they are ported from other environments. Users should not depend on the properties of the Alpha architecture to achieve source-level compatibility and portability between Tru64 UNIX for Alpha systems and other UNIX environments, except indirectly through high-level language facilities that are portable across architectures.

## 1.1 Applicability

This manual defines the rules and conventions that govern the **native user-mode run-time environment** on Tru64 UNIX systems running on Alpha hardware. The standard is applicable to all products in native user mode on the Tru64 UNIX operating system.

This standard applies to the following:

- All externally callable interfaces written in standard system software

- All intermodule calls to major software components

- All external procedure calls generated by language processors without benefit of interprocedural analysis or permanent private conventions, such as those for language support run-time library routines

## 1.2 Architectural Level

This Tru64 UNIX calling standard defines an **implementation-level run-time software architecture** for Tru64 UNIX operating systems running on Alpha hardware.

The interfaces, methods, and conventions specified in this document are primarily intended for use by implementors of compilers, debuggers, other run-time tools, run-time libraries, and other base operating system components. These specifications can be, but are not necessarily, appropriate for use by higher-level system and software applications.

Compilers and run-time libraries may provide additional support for these capabilities through interfaces that are more appropriate for compilers and applications. This standard neither prohibits nor requires such additional interfaces.

## 1.3 Goals

In general, this Tru64 UNIX calling standard promotes the highest degree of performance, portability, efficiency, and consistency in the interface between called procedures in the Tru64 UNIX environment.

The calling standard must be applicable to all intermodule callable interfaces in the native software system. The standard must consider the requirements of important compiled languages, including Ada, BASIC, C, C++, COBOL, FORTRAN, LISP, Pascal, PL/I, and calls to the operating system and library procedures. The needs of other languages that may be supported in the future must be met by the standard or by compatible revisions to it.

The goals of the Tru64 UNIX calling standard are to:

- Include capabilities specifically for lower-level components (such as assembler routines) that cannot be invoked from the high-level languages.

- Allow the calling program and called procedure to be written in different languages. The standard is designed to reduce the need to use language extensions for mixed-language programs.

- Contribute to the writing of error-free, modular, and maintainable software and promote effective sharing and reuse of software modules.

- Provide the programmer with control over the fixing and reporting of exception conditions and with management of the flow of control when various types of exception conditions occur.

- Add no space or time overhead to procedure calls and returns that do not

establish exception handlers. The standard is designed to minimize the

time overhead for establishing handlers at the cost of increasing time

overhead when exceptions occur.

- Be optimized for newer, more complex compilation techniques, such as interprocedural analysis and link-time code transformations. However, the standard is designed to require no such mechanisms for correctness.

- Provide support for a multilanguage, multithreaded execution environment.

- Provide an efficient mechanism for calling lightweight procedures that

do not need or want to pay the overhead of setting up a stack call frame.

(Procedures are referred to as lightweight because of their expedient way

of saving the call context.)

- Provide for the use of a common calling sequence to invoke lightweight

procedures that maintain only a register call frame and heavyweight

procedures that maintain a stack call frame. (Procedures that incur costs

by storing the call context in memory are referred to as heavyweight.)

This calling standard is designed to allow a compiler to determine whether to use a stack frame based on the complexity of the procedure being compiled. A recompilation of a called routine that causes a change in stack frame usage should not require a recompilation of its callers.

- Provide condition handling, traceback, and debugging for lightweight procedures that do not have a stack frame.

- Make efficient and effective use of the Alpha hardware architecture.

- Minimize the cost of procedure calls.

- Support a 64-bit address user-mode environment.

## 1.4 Requirements

The Tru64 UNIX calling standard was developed with the following requirements:

- All Alpha platforms must be able to implement the standard.

- Non-Digital compiler writers must be able to implement the standard.

- The standard must not require any complex compilation techniques (such as link-time code movement) for correctness.

## 1.5 Definitions

The following terms are used in the Tru64 UNIX calling standard:

address A 64-bit value used to denote a position in memory.

A vector of quadword entries that represents a argument list

procedure parameter list and possibly a function

value.

bound procedure A type of procedure that requires knowledge at run

time of a dynamically determined larger enclosing

scope to execute correctly.

call frame The body of information that a procedure must

> save to allow it to return properly to its caller. A call frame can exist on the stack or in registers. Optionally, a call frame can contain additional information required by the called procedure.

condition See exception condition.

#### descriptor

A mechanism for passing parameters, where the address of the descriptor is an entry in the argument list. The descriptor contains the parameter's address, data type, and size as well as additional information needed to describe fully the data passed.

# exception condition

An exceptional condition in the current hardware and/or software state that should be noted or fixed. The existence of this condition causes an interrupt in program flow and forces execution of out-of-line code. Such an event may be caused by exceptional hardware states (for example, arithmetic overflows or memory access control violations) or by actions performed by software (for example, subscript range checking, assertion checking, or asynchronous notification of one thread by another).

While the normal control flow is interrupted by an exception, the program flow is said to be in the **active** state.

#### exception handler

A procedure designed to handle exception conditions when they occur during the execution of a thread.

#### function

A procedure that returns a single value in accordance with the standard conventions for value returning. Additional values are returned by means of the argument list.

# hardware exception

A category of exceptions that directly reflects an exception condition in the current hardware state that should be noted or fixed by the software. Hardware exceptions can occur synchronously or asynchronously with respect to the normal program flow.

#### image

A collection of compiled modules that are combined by a linker into a form that can be loaded for execution.

#### immediate value

A mechanism for passing input parameters where the actual value is provided in the argument list entry by the calling program.

#### language support procedure

A procedure called implicitly to implement higher-level language constructs. Such procedures are not intended to be explicitly called from a user program.

## library procedure

A procedure explicitly called using the equivalent of a call statement or function reference. Such procedures are usually language-dependent.

## natural alignment

An attribute of certain data types that refers to the placement of the data so that the lowest addressed byte has an address that is a multiple of the size of the data in bytes. Natural alignment of an aggregate data type generally refers to an alignment in which all members of the aggregate are naturally aligned. This standard defines five natural alignments:

- byte Any byte address

- word Any byte address that is a multiple of 2

- longword Any byte address that is a multiple

- guadword Any byte address that is a multiple

- octaword Any byte address that is a multiple of 16

#### procedure

A closed sequence of instructions that is entered from and returns control to the calling program.

## procedure descriptor

A set of information about the properties of a procedure. This information is contained in data structures at run time to enable exception handling and unwinding to function properly.

#### procedure value

An address value that represents a procedure value. This value is the address of the first instruction of the procedure to be executed.

#### process

An address space containing at least one thread of execution. Selected security and quota checks are performed on a per-process basis.

This standard applies to the execution of multiple threads within a process. (An operating system that only provides a single thread of execution per process is considered a special case of a multithreaded system; that is, one where the maximum number of threads per process is 1.)

reference

A mechanism for passing parameters, where the calling program provides the parameter's address in the argument list.

sharable image

An image that can be shared by multiple processes. On Tru64 UNIX, a single copy of the image can be included simultaneously at different addresses in multiple using processes. Such an image is said to be position-independent.

signal

A POSIX-defined concept used to cause out-of-line execution of code.

standard call

A transfer of control to a procedure by any means that presents the called procedure with the environment defined by this standard and does not place additional restrictions, not defined in this standard, on the called procedure.

standard conforming procedure A procedure that adheres to all the relevant rules set forth in the Tru64 UNIX calling standard.

thread, or thread of execution

An entity scheduled for execution on a processor. In language terms, a thread is a computational entity utilized by a program unit such as a task, procedure, or loop. All threads executing within the same process share the same address space and other process context, but have unique per-thread hardware contexts that include machine registers such as program counters, process status, and stack pointers. This standard applies only to threads that execute within the context of a user-mode process and are scheduled on one or more processors according to software priority. All subsequent uses of the term **thread** in this standard refer only to these user-mode process threads.

#### thread-safe code

A property of code compiled in such a way as to ensure that it will execute properly when run in a threaded environment. Thread-safe code usually adds extra instructions to do certain run-time checks and requires that thread-local storage be accessed in a particular way.

#### undefined

Operations or behavior for which there is no directing algorithm used across all implementations that support the Tru64 UNIX calling standard. Such operations may or may not be well defined for a single implementation, but remain undefined with reference to this standard. The actions of undefined operations may not be required by standard-conforming procedures.

## unpredictable

Any results of an operation that cannot be guaranteed across all operating system implementations of the Alpha architecture calling standard. Regardless of whether these results are well-defined for a specific implementation of the Alpha calling standard, they remain unpredictable with reference to all implementations of the standard.

Therefore, all results caused by operations defined in the Tru64 UNIX implementation of the calling standard, but not specified as part of the calling standard are considered unpredictable. Standard-conforming procedures cannot depend on unpredictable results.

# **Tru64 UNIX Concepts**

This chapter describes some fundamental concepts of the Tru64 UNIX calling standard. The topics discussed are as follows:

- Address representation (Section 2.1)

- Procedure representation (Section 2.2)

- Register usage conventions (Section 2.3)

- Register names (Section 2.4)

- Program image layout (Section 2.5)

# 2.1 Address Representation

Values that represent addresses are 64 bits in size.

# 2.2 Procedure Representation

One of the distinguishing characteristics of any calling standard is how procedures are represented. The term used to denote the value that uniquely identifies a procedure is a **procedure value**. If the value identifies a bound procedure, it is called a **bound procedure value**.

In the Tru64 UNIX calling standard, a simple (not bound) procedure value is defined as the address of the first instruction of that procedure's entry code. (See Section 3.2.6.)

A bound procedure value is defined as the address of the first instruction of an instruction sequence that establishes the correct execution context for the bound procedure.

Procedures in the Tru64 UNIX calling standard are associated with a set of information called a procedure descriptor. This information describes various aspects of the procedure's code that are required for correct and robust exception handling. The exception processing described by this standard is based on the assumption that any given program counter value can be mapped to an associated procedure descriptor that describes the currently active procedure.

# 2.3 Register Usage Conventions

This section describes the usage of the Alpha hardware integer and floating-point registers.

# 2.3.1 Integer Registers

Table 2–1 describes the Alpha hardware integer registers.

Table 2-1: General-Purpose Integer Registers

| Register    | Description                                                                                                                                                                                                                                                                                                                                    |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| \$0         | Function value register. In a standard call that returns a nonfloating-point function result in a register, the result must be returned in this register. In a standard call, this register can be modified by the called procedure without being saved and restored.                                                                          |

| \$1 - \$8   | Conventional scratch registers. In a standard call, these registers can be modified by the called procedure without being saved and restored.                                                                                                                                                                                                  |

| \$9 - \$14  | Conventional saved registers. If a standard-conforming procedure modifies one of these registers, it must save and restore it.                                                                                                                                                                                                                 |

| \$15        | Stack frame base (FP) register. For procedures with a run-time variable amount of stack, this register is used to point at the base of the stack frame (fixed part of the stack). For all other procedures, this register has no special significance. If a standard-conforming procedure modifies this register, it must save and restore it. |

| \$16 - \$21 | Argument registers. In a standard call, up to six nonfloating-point items of the argument list are passed in these registers. In a standard call, these registers can be modified by the called procedure without being saved and restored.                                                                                                    |

| \$22 - \$25 | Conventional scratch registers. In a standard call, these registers can be modified by the called procedure without being saved and restored.                                                                                                                                                                                                  |

| \$26        | Return address (RA) register. In a standard call, the return address must be passed and returned in this register.                                                                                                                                                                                                                             |

| \$27        | Procedure value (PV) register. In a standard call, the procedure value of the procedure being called is passed in this register. (See Section 2.2.) In a standard call, this register can be modified by the called procedure without being saved and restored.                                                                                |

| \$28        | Volatile scratch register. The contents of this register are always <i>unpredictable</i> after any external transfer of control to or from a procedure. This unpredictable nature applies to both standard and nonstandard calls. This register can be used by the operating system for external call fixing, autoloading, and exit sequences. |

Table 2–1: General-Purpose Integer Registers (cont.)

| Register | Description                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| \$29     | Global pointer (GP) register. For a standard-conforming procedure, this register must contain the calling procedure's global offset table (GOT) segment pointer value at the time of a call and must contain the calling procedure's GOT segment pointer value or the called procedure's GOT segment pointer value upon return. This register must be treated as scratch by the calling procedure. (See Section 2.5 and Section 3.2.2 for details.) |

| \$30     | Stack pointer (SP) register. This register contains a pointer to the top of the current operating stack. Aspects of its usage and alignment are defined by the hardware architecture. See Section 3.2.1 for details about its usage and alignment.                                                                                                                                                                                                  |

| \$31     | ReadAsZero/Sink register. This register is defined in the hardware to be binary zero as a source operand or sink (no effect) as a result operand.                                                                                                                                                                                                                                                                                                   |

# 2.3.2 Floating-Point Registers

Table 2-2 describes the Alpha hardware floating-point registers.

Table 2–2: Floating-Point Registers

| Register      | Description                                                                                                                                                                                                                                                                                         |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| \$f0          | Floating-point function value register. In a standard call that returns a floating-point result in a register, this register is used to return the real part of the result. In a standard call, this register can be modified by the called procedure without being saved and restored.             |

| \$f1          | Floating-point function value register. In a standard call that returns a complex floating-point result in registers, this register is used to return the imaginary part of the result. In a standard call, this register can be modified by the called procedure without being saved and restored. |

| \$f2 - \$f9   | Conventional saved registers. If a standard-conforming procedure modifies one of these registers, it must save and restore it.                                                                                                                                                                      |

| \$f10 - \$f15 | Conventional scratch registers. In a standard call, these registers can be modified by the called procedure without being saved and restored.                                                                                                                                                       |

| \$f16 - \$f21 | Argument registers. In a standard call, up to six floating-point arguments can be passed by value in these registers. In a standard call, these registers can be modified by the called procedure without being saved and restored.                                                                 |

Table 2–2: Floating-Point Registers (cont.)

| Register      | Description                                                                                                                                       |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| \$f22 - \$f30 | Conventional scratch registers. In a standard call, these registers can be modified by the called procedure without being saved and restored.     |

| \$f31<br>     | ReadAsZero/Sink register. This register is defined in the hardware to be binary zero as a source operand or sink (no effect) as a result operand. |

## 2.4 Register Names

A few special register names appear in uppercase letters. This register naming convention is not necessarily followed by compiler or assembler tools that are used on Tru64 UNIX systems. However, a simple name substitution can convert from the notation used here to the appropriate convention. For example, the following code fragment might be used in conjunction with the standard C preprocessor as a prelude to the examples in this text:

```

#define FP

#define RA

#define PV

#define GP

$29

#define SP

```

# 2.5 Program Image Layout

The Tru64 UNIX calling standard defines only some aspects of an executable image. One basic concept that is defined involves program image layout, which permits optimal access to static data.

A hardware architecture in which instructions cannot contain full virtual addresses can be referred to as a base register architecture. The Alpha architecture is such an architecture. In a base register architecture, normal memory references within a limited range from a given address are expressed by using displacements relative to the contents of some register which contains that address (usually referred to as a **base register**). Base registers for external program segments, either data or code, are usually loaded indirectly through a program segment of address constants.

To optimize this base register access method, this standard requires each image that makes up an executable program to have zero or one global offset table (GOT). This global offset table can be further divided into multiple GOT segments. Together, the linker and the compilers arrange for various static data to be collected together into a minimal number of these GOT segments (typically one per image). During program execution, the GP (global pointer) register will contain a pointer into the appropriate GOT

segment so that all references therein can utilize a single base register. (For more information, see Section 3.2.2.)

During the compilation process, a compiler generates object language to designate data as belonging in a GOT segment. No single procedure is allowed to provide more than 64KB of data to a GOT segment. The linker pools these contributions to form the GOT segments. Typically, routines in several compilation units can share the same pointer into the GOT. In fact, if only one GOT segment is needed and will not exceed the 64KB addressing maximum, all routines within an image can use the same GOT pointer. Consequently, the GP register can be loaded once and then used by many routines to improve performance.

## Flow Control

This chapter contains descriptions of those aspects of the calling standard that deal with the flow of control in a program. This chapter does not discuss data manipulation. That topic is discussed in Chapter 4.

The following sections describe:

- Procedure types (Section 3.1)

- Transfer of control (Section 3.2)

## 3.1 Procedure Types

This Tru64 UNIX calling standard defines three basic procedures types. A compiler may choose which type to generate based on the requirements of the procedure in question. The standard procedure types are:

- Stack frame procedure

- A procedure that maintains its caller's context on the stack

- Register frame procedure

- A procedure that maintains its caller's context in registers

- Null frame procedure

- A procedure that executes in the context of its caller

Some procedures maintain their call frame on the stack; others maintain their call frame entirely in registers, although they may use the stack. Simple procedures do not necessarily maintain any call frame, but instead execute completely in the context of their caller. The calling procedure does not need to distinguish among these cases.

## 3.1.1 Procedure Descriptor Overview

Every procedure, other than a null procedure described in Section 3.1.4, must have a set of information associated with it that describes which type of procedure it is and what characteristics it has. This set of information, called a **procedure descriptor**, can be thought of as a single structure, although physically it is implemented by several structures. (See Chapter 8.) The procedure descriptor structure is used to interpret the call chain at any point during a thread's execution. The structure is normally built at compile

time and is not generally accessed at run time except in support of exception processing or other rarely used code execution.

Table 3-1 briefly summarizes the properties of a procedure that can be determined from its associated procedure descriptor. (Some fields apply to only certain kinds of procedures.) For a complete description of procedure descriptors, see Section 8.1.

Table 3-1: Procedure Properties Summary

| Procedure Property                | Description                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PDSC_FLAGS_REGISTER_FRAME         | Indicates a register (or null) frame procedure rather than a stack frame procedure.                                                                                                                                                                                                                                                                                                       |

| PDSC_FLAGS_BASE_REG_IS_FP         | Indicates that register \$15 is used as a frame pointer rather than as a preserved register.                                                                                                                                                                                                                                                                                              |

| PDSC_FLAGS_HANDLER_VALID          | Indicates that there is an associated exception handler.                                                                                                                                                                                                                                                                                                                                  |

| PDSC_FLAGS_EXCEPTION_MODE         | Indicates the error-reporting<br>behavior expected from certain called<br>mathematical library routines.                                                                                                                                                                                                                                                                                  |

| PDSC_FLAGS_EXCEPTION_FRAME        | Indicates that an operating system exception frame is included in the procedure's frame.                                                                                                                                                                                                                                                                                                  |

| PDSC_FLAGS_ARITHMETIC_SPECULATION | Indicates that arithmetic traps (SIGFPE) occurring in this procedure should not be delivered. This procedure was compiled with speculative execution optimization applied to arithmetic operations. Some arithmetic instructions have been moved backward, preceding conditional branches that used to control their effects. Traps caused by these moved instructions should be ignored. |

Table 3-1: Procedure Properties Summary (cont.)

| Procedure Property          | Description                                                                                                                                                                                                                                                                                                                                                                                                |  |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PDSC_CRD_MEMORY_SPECULATION | Indicates that memory traps (SIGSEGV, SIGBUS) occurring in this procedure should not be delivered. This procedure was compiled with speculative execution optimization applied to memory reference operations. Some memory reference instructions have been moved backward, preceding conditional branches that used to control their effects. Traps caused by these moved instructions should be ignored. |  |

| PDSC_RPD_RSA_OFFSET         | Specifies an offset from the stack pointer (SP) or frame pointer (FP) register to the register save area.                                                                                                                                                                                                                                                                                                  |  |

| PDSC_RPD_IMASK              | Indicates a bit mask for the general registers that are saved in the stack.                                                                                                                                                                                                                                                                                                                                |  |

| PDSC_RPD_FMASK              | Indicates a bit mask for the floating-point registers that are saved in the stack.                                                                                                                                                                                                                                                                                                                         |  |

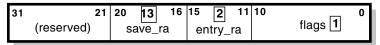

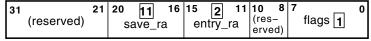

| PDSC_RPD_ENTRY_RA           | Indicates the register that contains the return address at the time of a call.                                                                                                                                                                                                                                                                                                                             |  |

| PDSC_RPD_SAVE_RA            | Indicates the register in which the return address is saved when it is not saved on the stack.                                                                                                                                                                                                                                                                                                             |  |

| PDSC_RPD_FRAME_SIZE         | Specifies the size of the fixed part of the stack frame.                                                                                                                                                                                                                                                                                                                                                   |  |

| PDSC_RPD_SP_SET             | Specifies the offset from the beginning of the procedure to the instruction that changes the stack pointer.                                                                                                                                                                                                                                                                                                |  |

| PDSC_RPD_ENTRY_LENGTH       | Specifies the length of the procedure prologue.                                                                                                                                                                                                                                                                                                                                                            |  |

| PDSC_CRD_BEGIN_ADDRESS      | Specifies the address of the first instruction and entry point of the procedure.                                                                                                                                                                                                                                                                                                                           |  |

| PDSC_RPD_HANDLER_ADDRESS    | Specifies the address of an associated exception handling procedure.                                                                                                                                                                                                                                                                                                                                       |  |

| PDSC_RPD_HANDLER_DATA       | Specifies supplementary per-procedure data to be passed to an associated exception handler.                                                                                                                                                                                                                                                                                                                |  |

## 3.1.2 Stack Frame Procedure

A **stack frame procedure** is one that allocates space for and saves its caller's context on the stack. This type of procedure is sometimes called a "heavyweight procedure" because of the cost of storing this context in memory. These procedures can save and restore registers and may make standard calls to other procedures.

The stack frame of this type of procedure consists of a fixed part (the size of which is known at compile time) and an optional variable part. Certain optimizations can be done if the optional variable part is not present. Compilers must be careful to recognize situations that can effectively cause a variable part of the stack to exist in nonintuitive ways; for example, when a called routine uses the stack as a means to return certain types of function values. (See Section 4.1.7 for details.)

If such a situation exists, a compiler must choose to use a variable-size stack frame procedure when compiling the caller so that any unwind operations can be performed correctly.

#### 3.1.2.1 Stack Frame Format

Even though the exact contents of a stack frame are determined by the compiler, there are certain properties common to all stack frames. There are two basic types of stack frames: fixed-size and variable-size. Some parts of the stack frame are optional and occur only as required by the particular procedure. In the figures, brackets ([]) surrounding a field's name indicate that the field is optional.

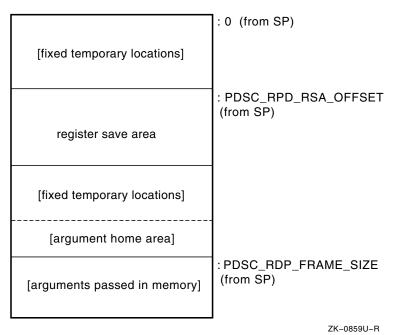

Figure 3–1 shows the format of the stack frame for a procedure with a fixed amount of stack. This format uses SP as the stack base register (that is, PDCS\_FLAGS\_BASE\_REG\_IS\_FP is 0). In this case, \$15 is simply another saved register and has no special significance.

Figure 3-1: Fixed Size Stack Frame Format

octaword-aligned

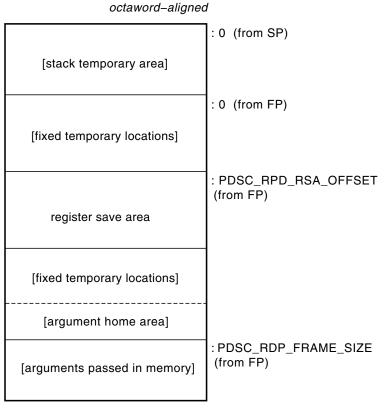

Figure 3–2 shows the format of the stack frame for a procedure with a varying amount of stack. The format uses FP as the stack base register; that is,  $PDSC_FLAGS_BASE_REG_IS_FP$  is 1.

Figure 3-2: Variable Size Stack Frame Format

ZK-0860U-R

In both cases, the portion of the stack frame designated by PDSC\_RPD\_FRAME\_SIZE must be allocated and initialized by the entry code sequence of a called procedure with a stack frame.

**Fixed temporary locations** are optional sections of the stack frame that contain language-specific locations required by the procedure context of some high-level languages. These locations might include, for example, register spill areas, language-specific exception handling contexts (such as language dynamic exception handling information), or fixed temporary locations.

If a compiler chooses, the fixed temporary locations adjacent to the area pointed to by the frame base register added to the value of PDSC\_RPD\_FRAME\_SIZE can be used for a special purpose referred to as the argument home area.

The **argument home area** is a region of memory used by the called procedure for the purpose of assembling in contiguous memory the arguments passed in registers adjacent to the arguments passed in memory,

so that all arguments can be addressed as a contiguous array. This area can also be used to store arguments that are passed in registers if an address for such an argument must be generated. Generally, 6 or 12 contiguous quadwords of stack storage are allocated by the called procedure for this kind of storage. (See Section 4.1.3 for details.)

The **register save area** is a set of consecutive quadwords where the current procedure saves and restores registers. The register save area begins at the location pointed to by the frame base register (as indicated by PDSC\_FLAGS\_BASE\_REG\_IS\_FP) added to the value of the contents of PDSC\_RPD\_RSA\_OFFSET. The result must be a quadword-aligned address. The set of registers saved in this area contains the return address followed by the registers specified in the procedure descriptor by PDSC\_FLAGS\_IMASK and PDSC\_FLAGS\_FMASK. The details of how to lay out and populate the register save area are described in Section 3.1.2.2.

A compiler can use the **stack temporary area** for storage of fixed local variables, such as constant-sized data items, program state information, and dynamically sized local variables. The stack temporary area can also be used for dynamically sized items with a limited lifetime, such as a dynamically sized function result or string concatenation that cannot be directly stored in a target variable. When a procedure uses this area, the compiler must keep track of its base and reset SP to that base in order to reclaim storage used by temporaries.

The high-address end of the stack frame is defined by the value stored in PDSC\_RPD\_FRAME\_SIZE added to the contents of the SP or FP register, as indicated by PDSC\_FLAGS\_BASE\_REG\_IS\_FP. The high-address end is used to determine the value of the SP register for the predecessor procedure in the call chain.

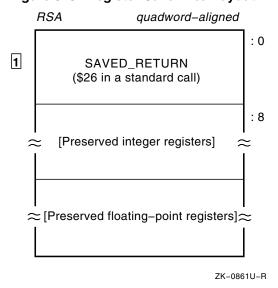

#### 3.1.2.2 Register Save Area

The layout of the frame of a stack frame procedure contains a substructure called the **register save area**. This section describes how this area is defined and populated.

All registers saved in the variable portion of the register save area must have the corresponding bit set to 1 in the appropriate procedure descriptor register save mask. This bit must be set to 1 even if the register is not a member of the set of registers required to be saved across a standard call. If the bit is not set to 1, the offsets within the save area cannot be calculated correctly.

The algorithm for packing saved registers in the quadword-aligned register save area is as follows:

• The return address is saved at the lowest address of the register save area, offset 0.

- All saved integer registers ,as indicated by the corresponding bit in PDSC RPD IMASK being set to 1, are stored, in register-number order, in consecutive quadwords beginning at offset 8 of the register save area.

- All saved floating-point registers, as indicated by the corresponding bit in PDSC RPD FMASK being set to 1, are stored, in register-number order, in consecutive quadwords following the saved integer registers.

|       | Nista |  |

|-------|-------|--|

| 14016 | Note  |  |

A floating-point register saved in the stack is stored as a 64-bit exact image of the register; that is, no bit reordering is done in the process of moving the data to or from memory. Compilers must use an stt instruction to store the register regardless of the floating-point type.

This behavior is required so that an unwind routine can properly restore the floating-point registers without more complete type information.

A standard-conforming procedure that utilizes a register save area must save the return address register at offset 0 in the register save area. There is no corresponding bit in the register save mask for this register slot.

Figure 3–3 shows the layout of the register save area.

Figure 3-3: Register Save Area Layout

$\fbox{1}$  RSA.SAVED\_RETURN is the contents of the return address register.

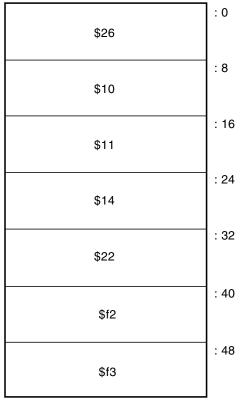

For example, if registers \$10, \$11, \$14, \$22, \$f2, and \$f3 are saved by a standard-conforming procedure, the PDSC\_RPD\_IMASK value is 00404C00 (hex) and the PDSC\_RPD\_FMASK is 0000000C (hex). The register save area for such a procedure is packed as shown in Figure 3–4.

Figure 3-4: Register Save Area Example

quadword-aligned

ZK-0862U-R

### 3.1.3 Register Frame Procedure

A **register frame procedure** does not maintain a call frame on the stack and must, therefore, save its caller's context in registers. This type of procedure is sometimes referred to as a "lightweight procedure" because of the relatively fast way it saves the call context.

Such a procedure cannot save and restore nonscratch registers. Because a procedure without a stack frame must, therefore, use scratch registers to maintain the caller's context; such a procedure cannot make a standard-conforming call to any other procedure.

A procedure with a register frame can have an exception handler and can handle exceptions in the normal way. Such a procedure can also allocate local stack storage in the normal way, although it might not necessarily do so.

| <br>Note |  |

|----------|--|

| <br>Note |  |

Lightweight procedures have more freedom than might be apparent. By the use of appropriate agreements with callers of the lightweight procedure as well as with procedures that the lightweight procedure calls, and by the use of unwind handlers, a lightweight procedure can modify nonscratch registers and can call other procedures.

Agreements such as these can be made by convention (as in the case of language-support routines in the run-time library) or by interprocedural analysis. Calls employing such agreements are, however, not standard calls, and might not be fully supported by a debugger because it might not be able to find the contents of the preserved registers, for example.

Because such agreements must be permanent for upward compatibility of object code, lightweight procedures should, in general, follow the normal restrictions.

#### 3.1.4 Null Frame Procedure

A **null frame procedure** is a simple case of a register frame procedure. The null frame procedure has the following characteristics:

- The entry return address register is \$26 (PDSC RPD ENTRY RA = 26).

- The return address is not saved in any other register (PDSC RPD SAVE RA = PDSC RDP ENTRY RA).

- No stack space is allocated (PDSC\_RPD\_SP\_SET = 0 and PDSC\_RPD\_FRAME\_SIZE = 0).

- As a result of these characteristics, the prologue requires no instructions (PDSC RPD ENTRY LENGTH = 0).

- There is no associated exception handler (PDSC\_RPD\_HANDLER\_ADDRESS = 0).

This special case of a register frame procedure is of interest because it has an associated special-case procedure descriptor representation. (See Section 8.1 for information about procedure descriptor representation.)

# 3.2 Transfer of Control

A standard-conforming procedure call can use any sequence of instructions that presents the called routine with the required environment. (See the standard call definition in Section 1.5.) However, the majority of standard-conforming external calls is performed with a common sequence

of instructions and conventions. This common set of call conventions is so pervasive that it is included as part of this standard in Section 3.2.1.

This calling standard has been designed so that the same instruction sequence can be used to call each different type of procedure; that is, the caller does not have to know which type of procedure is being called.

#### 3.2.1 Call Conventions

The following call conventions describe the rules and methods used to communicate certain information between the caller and the called procedure during invocation and return:

#### procedure value

The calling procedure must pass the procedure value of the called procedure to the called procedure. This value can be a statically or dynamically bound procedure value. To pass this value, the calling procedure must load \$27 with the procedure value before control is transferred to the called procedure. (See Section 2.2 for a description of procedure values.)

When a target routine is not loaded in memory at the beginning of execution of a main program or shared image, the procedure value used by a caller of that routine generally addresses some kind of stub or jacket routine. The purpose of a stub or jacket routine is to perform the loading of the actual target routine. The call is completed after this load operation.

When control actually reaches the target routine entry point, \$27 must contain the actual procedure value of the newly loaded routine as if no intermediate processing had occurred. Subject to these constraints, the PV register can be used freely by the stub/jacket code as a temporary register during its own execution.

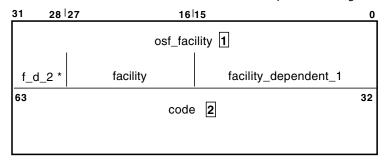

#### return address