**SPARC**book<sup>TM</sup>

SPARCbook 1

Technical Reference Manual

IADPOLE

# SPARCbook 1 Technical Reference Manual

Tadpole Technology Inc 12012 Technology Blvd. Austin, TX 78727 USA

Tel: 512-219-2200 Fax: 512-219-2222 Tadpole Technology plc Cambridge Science Park Milton Road Cambridge, CB4 4WQ ENGLAND

> Tel: 0223 250030 Fax: 0223 250036

#### **FCC Class B Notice**

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- · Reorient or relocate the receiving antenna

- Increase the separation between the equipment and receiver

- Connect the equipment into an outlet on a circuit different from that to which the receiver is connected

- Consult your supplier, or an experienced radio or television technician for help

#### Modifications

This equipment contains no user-serviceable parts. You are advised that unauthorized changes or modifications to the equipment could cause it to exceed Class B limits and may void the authority granted by the FCC to operate the equipment.

#### **Shielded Cables**

Connections between the SPARCbook and any connected peripherals must be made using shielded cables to maintain compliance with FCC radio frequency emission limits.

#### **FCC Part 68 Modem Information**

This equipment complies with Part 68 of the FCC rules. On the underside of this equipment is a label that contains, among other information, the FCC registration number and ringer equivalence number (REN) for this equipment. If requested, this information must be provided to the telephone company.

This equipment uses the following USOC jacks: RJ11C

The REN is used to determine the quantity of devices which may be connected to the telephone line. Excessive RENs on the telephone line may result in the devices not ringing in response to an incoming call. In most, but not all areas, the sum of the RENs should not exceed five (5.0). To be certain of the number of devices that may be connected to the line, as determined by the total RENs, contact the telephone company to determine the maximum REN for the calling area.

If this equipment causes harm to the telephone network, the telephone company will notify you in advance that temporary discontinuance of service may be required. If advance notice is not practical, the telephone company will notify the customer as soon as possible. Also, you will be advised of your right to file a complaint with the FCC if you believe it is necessary.

The telephone company may make changes in its facilities, equipment, operations or procedures that could affect the operation of the equipment. If this happens, the telephone company will provide advance notice in order for you to make the necessary modifications in order to maintain uninterrupted service.

If trouble is experienced with this equipment, please contact Tadpole Technology Inc, 8310 Capital of Texas Highway North, Austin, Texas 78731 Tel: (512) 338 4221 for repair and/or warranty information. If the trouble is causing harm to the telephone network, the telephone company may request you remove the equipment from the network until the problem is resolved.

The following repairs can be done by the customer: None

This equipment cannot be used on telephone company-provided coin service. Connection to Party Line Service is subject to state tariffs.

#### Trademarks

All rights reserved. This product or document is protected by copyright and distributed under licenses restricting its use, copyring, distribution and decompilation. No part of this product or document may be reproduced in any form by any means without prior written authorization of Sun and its licensors, if any. This product or the products depicted herein may be protected by one or more U.S. or international patents or pending patents. Portions of this product may be derived from the UNIX® and Berkeley 4.3 BSD systems, licensed from UNIX Systems Laboratories, Inc. and the University of California, respectively. Third party font software in this product is protected by copyright and licensed from Sun's Font Suppliers.

RESTRICTED RIGHTS LEGEND: Use, duplication, or disclosure by the government is subject to restrictions as set forth in subparagraph (c) (1) (ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013 and FAR 52.227-19.

Sun, Sun Microsystems, the Sun Logo, OpenWindows, SunView, SunOS, X-11 NEWS, DeskSet, NFS and NEWS are trademarks or registered trademarks of Sun Microsystems, Inc. UNIX and OPEN LOOK are registered trademarks of UNIX Systems Laboratories, Inc. All other product names mentioned herein are the trademarks of their respective owners. All SPARC trademarks, including the SCD Compliant Logo, are trademarks or registered trademarks of SPARC International, Inc. The SPARCbook trademark is licensed exclusively to Tadpole Technology, Inc. Products bearing SPARC trademarks are based upon an architecture developed by Sun Microsystems. Inc.

The OPEN LOOK® and Sun™ Graphical User Interfaces were developed by Sun Microsystems, Inc. for its users and licensees. Sun acknowledges the pioneering efforts of Xerox in researching and developing the concept of visual or graphical user interfaces for the computer industry. Sun holds a non-exclusive license from Xerox to the Xerox Graphical User Interface, which license also covers Sun's licensees who implement OPEN LOOK GUI's and otherwise comply with Sun's written license agreements.

The X Window System is a product of the Massachusetts Institute of Technology.

UNIX and OPEN LOOK are registered trademarks of UNIX System Laboratories PostScript is a trademark of Adobe Systems, Inc Sendfax is a registered trademark of Sierra Semiconductor Corp SoftPC is a registered trademark of Insignia Solutions Ltd

Issue A of January 1992 Part Number: 980 011 ©1992 by Tadpole Technology Printed in the UK

# **CONTENTS**

| INTRODUCTION TO                              |           |

|----------------------------------------------|-----------|

| THE SPARCbook TECHNICAL REFERENCE MAN        | UAL9      |

| MANUAL STRUCTURE                             |           |

| INDENTED AUDIENCE                            |           |

| CONVENTIONS USED IN THIS DOCUMENT            | 11        |

| Logic States                                 |           |

| Data Length Definitions                      |           |

| CHAPTER ONE                                  |           |

| OVERVIEW                                     | 13        |

| CENTRAL PROCESSOR                            |           |

| MAIN MEMORY                                  |           |

| DISPLAY                                      |           |

| UNIVERSAL PERIPHERAL CONTROLLER              |           |

| MICROCONTROLLER SUBSYSTEM                    | 17        |

| ETHERNET INTERFACE                           |           |

| MODEM                                        |           |

| REAL TIME CLOCK AND EPROM                    | <i>18</i> |

| SPARCBOOK TECHNICAL SPECIFICATION            |           |

| SPARCBOOK DETAILED ADDRESS MAP               | 22        |

| DRAM                                         | 22        |

| Display Controller                           | 22        |

| Ethernet Controller                          | 23        |

| Modem Interface                              | 24        |

| Real Time Clock / SRAM                       | 24        |

| 16-Bit I/O Region - Hard Disk Data Interface | 24        |

| 8-Bit I/O Region - UPC Associated Interfaces | 25        |

| MPI ASIC                                     | 26        |

| CHAPTER TWO                                  |           |

| ARCHITECTURE                                 | 27        |

| BUS STRUCTURE                                | 28        |

| Mbus                                         | 28        |

| Pbus                                         | 28        |

| Mhus - Phus Interface                        | 29        |

| CHAPIER IHREE                                              |            |

|------------------------------------------------------------|------------|

| THE SPARC CPU MODULE                                       | 31         |

| CY7C601A INTEGER UNIT                                      | 32         |

| Instructions Overview                                      | 32         |

| CY7C601A Internal Registers                                | 34         |

| Traps and Interrupts                                       | <i>3</i> 8 |

| Memory Protection                                          | <i>3</i> 8 |

| FLOATING POINT UNIT                                        | 40         |

| Overview                                                   | 40         |

| Floating Point Registers                                   | 40         |

| Floating-Point State Register                              | 41         |

| CACHE CONTROLLER AND MEMORY MANAGEMENT UNIT                | 43         |

| Memory Management Unit                                     | 43         |

| Cache Controller                                           | 47         |

| CY7C157A CACHE STORAGE UNIT                                | 49         |

| CHAPTER FOUR                                               |            |

| MAIN MEMORY                                                | 51         |

| FUNCTIONAL DESCRIPTION                                     |            |

| CHAPTER 5                                                  |            |

| MBUS TO PBUS INTERFACE                                     | 53         |

| INTRODUCTION TO THE MPI                                    |            |

| PERIPHERAL BUS INTERFACE                                   | 54         |

|                                                            |            |

| Direct OperationFIFO Operations                            | 54         |

| Peripheral Space Address Decoder                           |            |

| COUNTER-TIMERS                                             |            |

| System Timers                                              |            |

| Bus Timeout Timer                                          |            |

| SERIAL I/O PORT                                            |            |

| Serial Input                                               |            |

| Serial Output                                              |            |

| POWER MANAGEMENT FUNCTIONS                                 | 61         |

| Clock Control                                              |            |

| INTERRUPT CONTROLLER                                       |            |

|                                                            |            |

| INTERNAL REGISTERS                                         |            |

| FIFO Control Registers                                     |            |

| Timer Control Registers POWER MANAGEMENT CONTROL REGISTERS |            |

| Interrupt Control Registers                                |            |

| 11861 BU COULU REVISEIS                                    |            |

| Serial Input/Output Registers                                                                                                                                                                                                                                                                                       | 71                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Software Reset Register                                                                                                                                                                                                                                                                                             | 72                   |

| Error Status Register                                                                                                                                                                                                                                                                                               | 73                   |

| CHAPTER SIX                                                                                                                                                                                                                                                                                                         |                      |

| MICROCONTROLLER SUBSYSTEM                                                                                                                                                                                                                                                                                           | 75                   |

| KEYBOARD INTERFACE                                                                                                                                                                                                                                                                                                  |                      |

| Key Repeat                                                                                                                                                                                                                                                                                                          |                      |

| Special Characters                                                                                                                                                                                                                                                                                                  | 77                   |

| Special Routines                                                                                                                                                                                                                                                                                                    | 77                   |

| MOUSEKEY INTERFACING                                                                                                                                                                                                                                                                                                | <i>78</i>            |

| Mousekey Initialization                                                                                                                                                                                                                                                                                             |                      |

| Mousekey Events                                                                                                                                                                                                                                                                                                     |                      |

| HARDWARE INTERFACES                                                                                                                                                                                                                                                                                                 | 80                   |

| Host Instruction Protocol                                                                                                                                                                                                                                                                                           |                      |

| Host Interrupts                                                                                                                                                                                                                                                                                                     |                      |

| EEPROM Data                                                                                                                                                                                                                                                                                                         |                      |

| CHAPTER SEVEN                                                                                                                                                                                                                                                                                                       |                      |

| INIVEDGAL DEDIDUEDAL CONTROLLED                                                                                                                                                                                                                                                                                     | 05                   |

| UNIVERSAL PERIPHERAL CONTROLLER                                                                                                                                                                                                                                                                                     |                      |

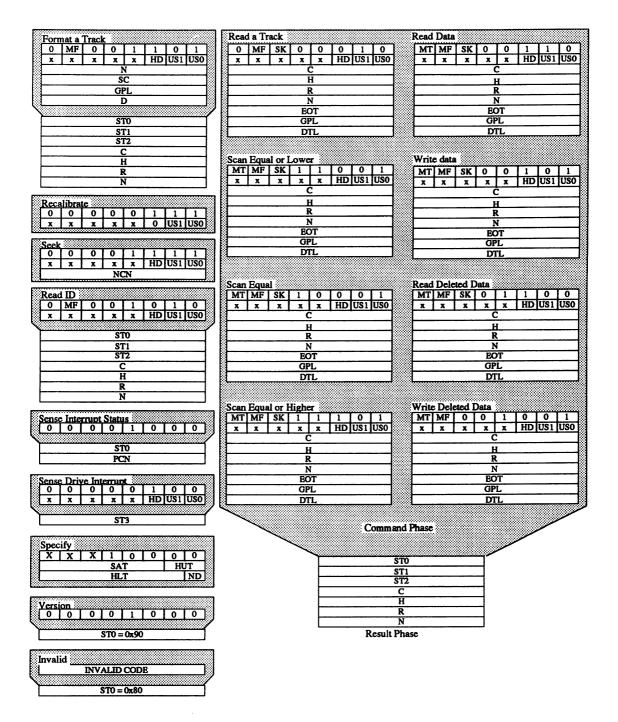

| FLOPPY DISK CONTROLLER                                                                                                                                                                                                                                                                                              | 86                   |

| FLOPPY DISK CONTROLLER                                                                                                                                                                                                                                                                                              | 86<br>86             |

| FLOPPY DISK CONTROLLER                                                                                                                                                                                                                                                                                              | 86<br>86<br>87       |

| FLOPPY DISK CONTROLLER  Host Interface Floppy Disk Commands  FDC Operating Modes                                                                                                                                                                                                                                    | 86<br>86<br>87<br>89 |

| FLOPPY DISK CONTROLLER  Host Interface Floppy Disk Commands  FDC Operating Modes  IDE HARD DISK INTERFACE                                                                                                                                                                                                           | 86<br>86<br>87<br>89 |

| FLOPPY DISK CONTROLLER  Host Interface Floppy Disk Commands  FDC Operating Modes  IDE HARD DISK INTERFACE  IDE Overview                                                                                                                                                                                             | 86<br>87<br>89<br>89 |

| FLOPPY DISK CONTROLLER  Host Interface Floppy Disk Commands FDC Operating Modes IDE HARD DISK INTERFACE IDE Overview IDE Interface Operating Modes                                                                                                                                                                  |                      |

| FLOPPY DISK CONTROLLER  Host Interface Floppy Disk Commands  FDC Operating Modes  IDE HARD DISK INTERFACE  IDE Overview  IDE Interface Operating Modes  Task File Registers                                                                                                                                         |                      |

| FLOPPY DISK CONTROLLER  Host Interface Floppy Disk Commands FDC Operating Modes  IDE HARD DISK INTERFACE  IDE Overview  IDE Interface Operating Modes  Task File Registers  IDE Command Summary                                                                                                                     |                      |

| FLOPPY DISK CONTROLLER  Host Interface Floppy Disk Commands FDC Operating Modes  IDE HARD DISK INTERFACE  IDE Overview  IDE Interface Operating Modes  Task File Registers  IDE Command Summary  PARALLEL PORT                                                                                                      |                      |

| FLOPPY DISK CONTROLLER  Host Interface  Floppy Disk Commands  FDC Operating Modes  IDE HARD DISK INTERFACE  IDE Overview  IDE Interface Operating Modes  Task File Registers  IDE Command Summary  PARALLEL PORT  Printer Interface Registers                                                                       |                      |

| FLOPPY DISK CONTROLLER  Host Interface Floppy Disk Commands FDC Operating Modes  IDE HARD DISK INTERFACE  IDE Overview IDE Interface Operating Modes Task File Registers IDE Command Summary PARALLEL PORT Printer Interface Registers MOUSE PORT                                                                   |                      |

| FLOPPY DISK CONTROLLER  Host Interface  Floppy Disk Commands  FDC Operating Modes  IDE HARD DISK INTERFACE  IDE Overview  IDE Interface Operating Modes  Task File Registers  IDE Command Summary  PARALLEL PORT  Printer Interface Registers                                                                       |                      |

| FLOPPY DISK CONTROLLER  Host Interface Floppy Disk Commands FDC Operating Modes  IDE HARD DISK INTERFACE  IDE Overview  IDE Interface Operating Modes  Task File Registers  IDE Command Summary  PARALLEL PORT  Printer Interface Registers  MOUSE PORT  Mouse Port Registers  SERIAL PORT                          |                      |

| FLOPPY DISK CONTROLLER  Host Interface Floppy Disk Commands FDC Operating Modes IDE HARD DISK INTERFACE IDE Overview IDE Interface Operating Modes Task File Registers IDE Command Summary PARALLEL PORT Printer Interface Registers MOUSE PORT Mouse Port Registers                                                |                      |

| FLOPPY DISK CONTROLLER  Host Interface  Floppy Disk Commands  FDC Operating Modes  IDE HARD DISK INTERFACE  IDE Overview  IDE Interface Operating Modes  Task File Registers  IDE Command Summary  PARALLEL PORT  Printer Interface Registers  MOUSE PORT  Mouse Port Registers  SERIAL PORT  Serial Port Registers |                      |

| CHAPTER EIGHT                               |             |

|---------------------------------------------|-------------|

| MODEM                                       | 107         |

| MODEM OVERVIEW                              |             |

| INTERFACE CONTROL                           | 109         |

| MAC Integral UART Registers                 |             |

| THE AT COMMAND SET                          | 111         |

| Basic Command Set                           | 112         |

| Sendfax Command Set                         |             |

| S-REGISTERS                                 | 115         |

| FAX RESPONSES                               | 116         |

| CHAPTER NINE                                |             |

| ETHERNET INTERFACE                          | 119         |

| NETWORKING OVERVIEW                         |             |

| Ethernet Protocol                           |             |

| Basic Operations                            | 121         |

| THE SPARCBOOK ETHERNET IMPLEMENTATION       | 122         |

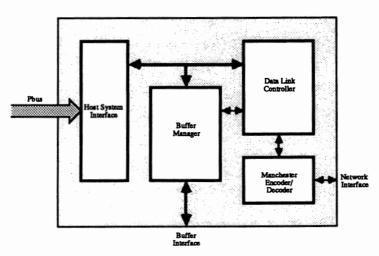

| FUNCTIONAL DESCRIPTION OF THE NICE          | 123         |

| NICE Host System Interface                  | 124         |

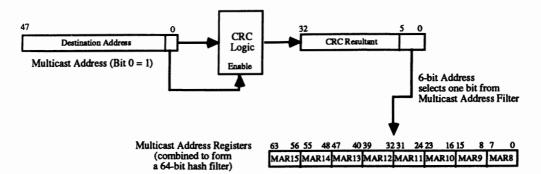

| Buffer Manager                              | 126         |

| INTERRUPTS                                  | 128         |

| CHAPTER TEN                                 |             |

| DISPLAY CONTROLLER                          | 129         |

| DISPLAY INTERFACE OVERVIEW                  | 130         |

| HOST INTERFACE                              |             |

| Host Accesses to the Color Lookup Table     |             |

| Display Access to Video Memory              |             |

| INTERNAL RAMDAC OPERATION                   |             |

| SIMULTANEOUS DISPLAY ENABLING               | 133         |

| INTELLIGENT POWER MANAGEMENT AND SEQUENCING | 133         |

| CHAPTER ELEVEN                              |             |

| MK48T02 BATTERY BACKED                      |             |

| REAL TIME CLOCK AND SRAM                    |             |

| BATTERY BACKED SRAM                         | <i>13</i> 8 |

| REAL TIME CLOCK                             | <i>13</i> 8 |

| RTC Operation                               | 139         |

| Peal Time Clock Calibration                 |             |

| CHAPTER TWELVE                               |     |

|----------------------------------------------|-----|

| S1-BASE SCHEMATICS DESCRIPTION               | 141 |

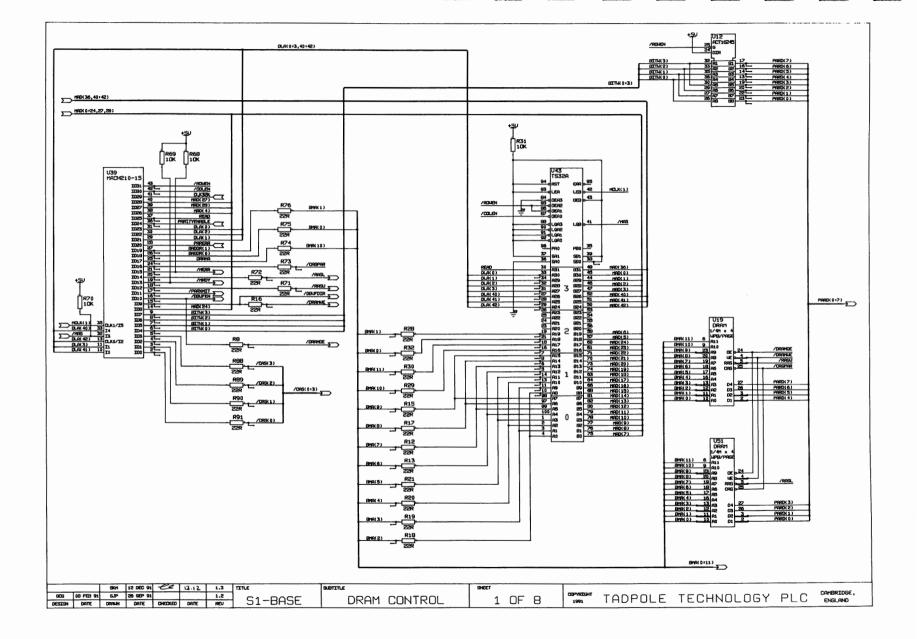

| Sheet 1 - DRAM CONTROL                       | 141 |

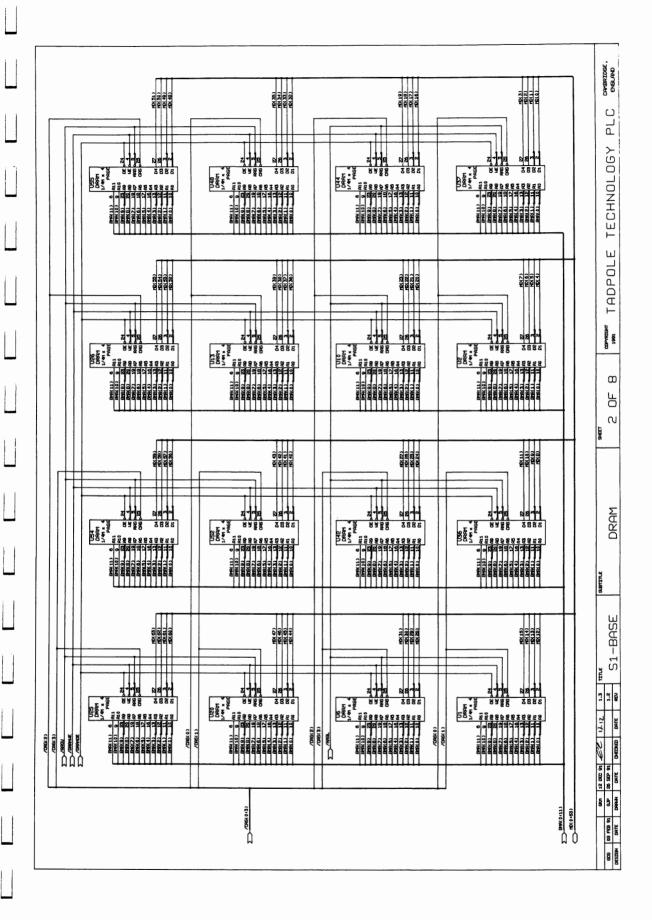

| Sheet 2 - DRAM                               | 142 |

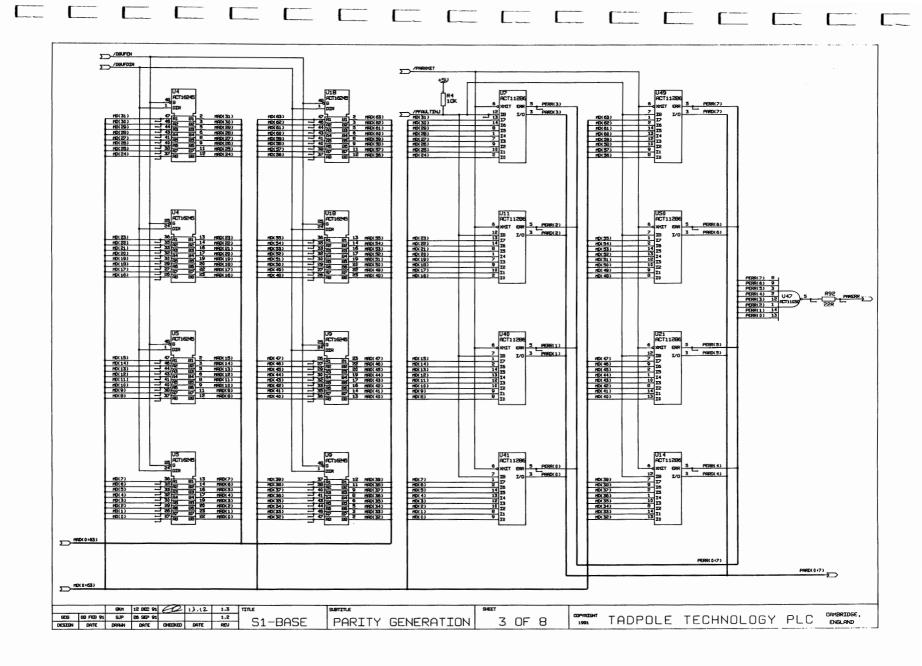

| Sheet 3 - PARITY GENERATION                  | 142 |

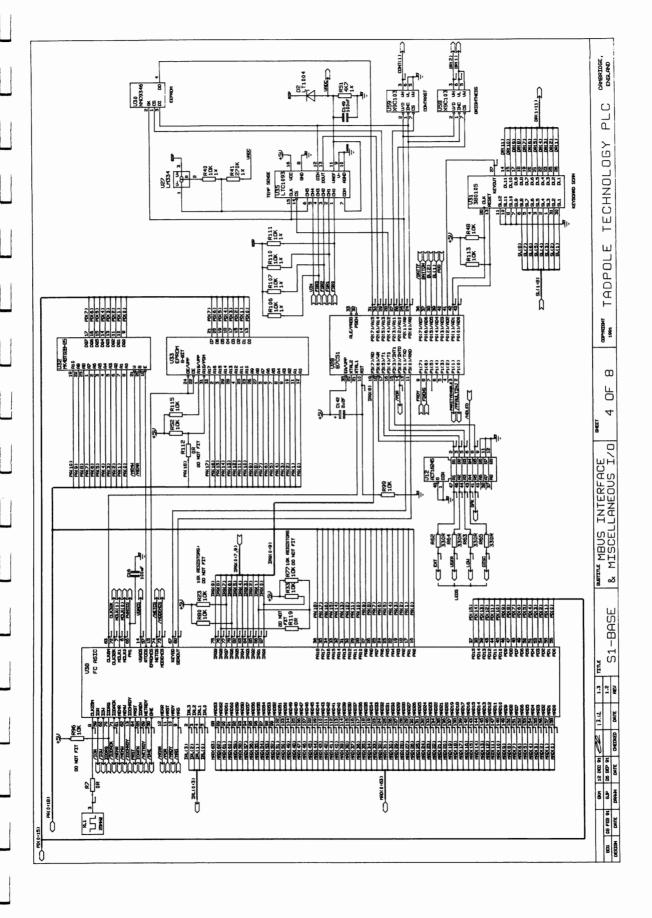

| Sheet 4 - MBUS INTERFACE & MISCELLANEOUS I/O | 143 |

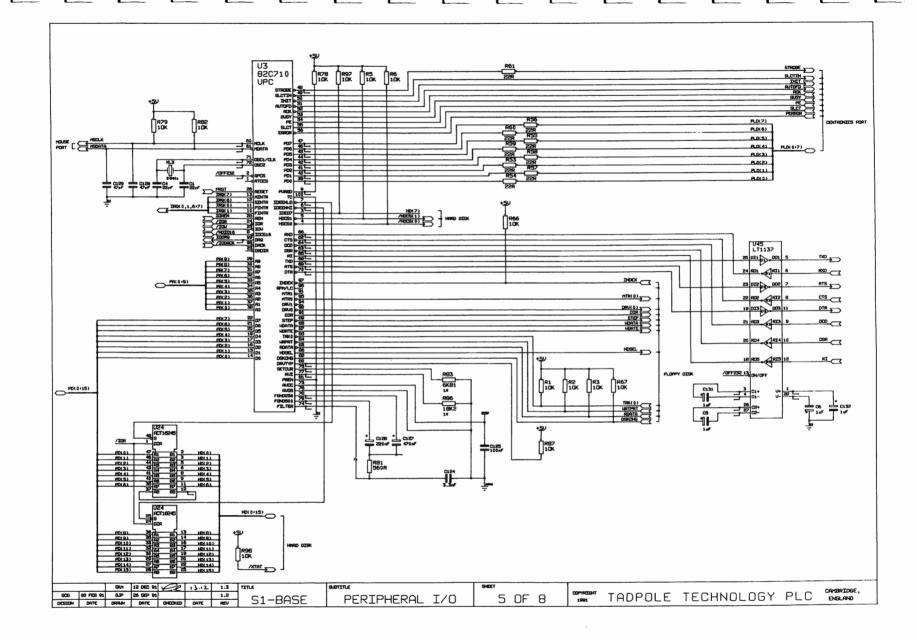

| Sheet 5 - PERIPHERAL I/O                     |     |

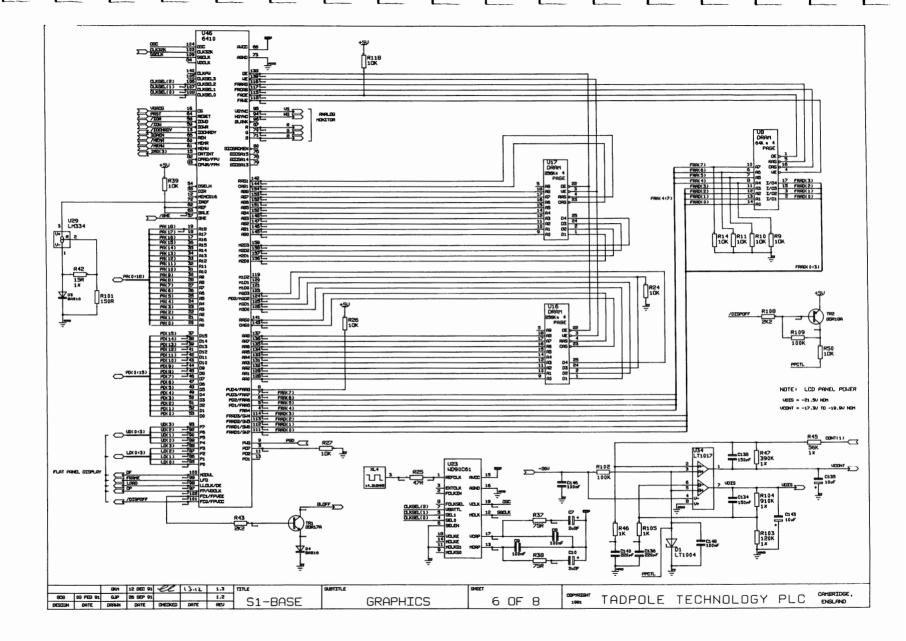

| Sheet 6 - GRAPHICS                           | 145 |

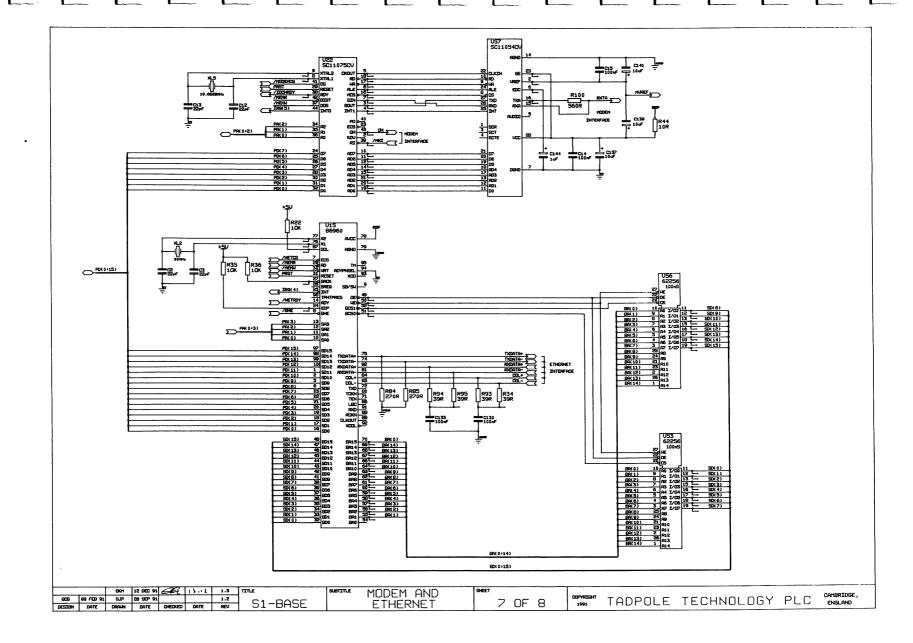

| Sheet 7 - MODEM AND ETHERNET                 | 145 |

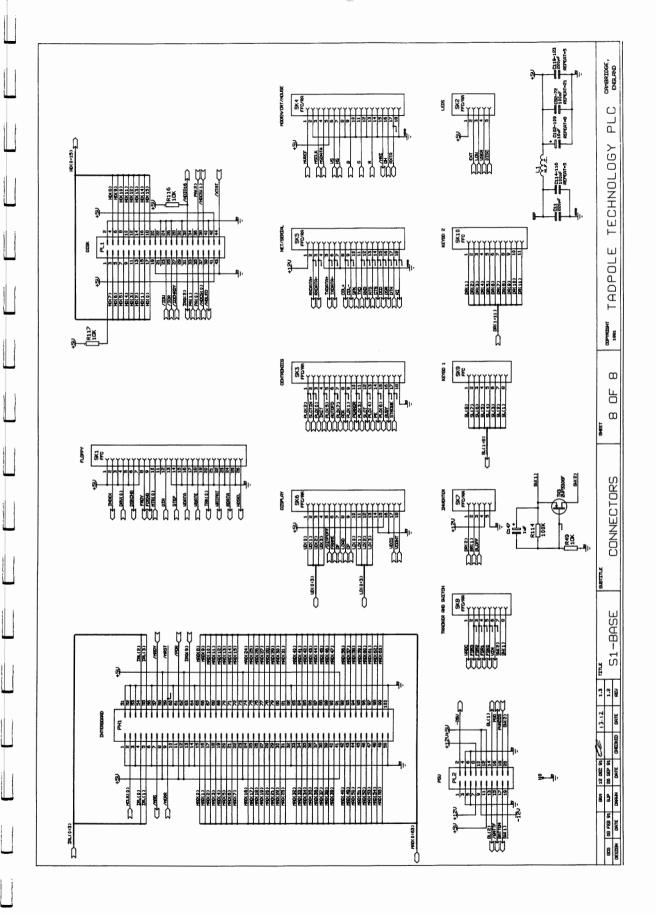

| Sheet 8 - CONNECTORS                         | 146 |

| Color Systems only - Sheet 9                 | 146 |

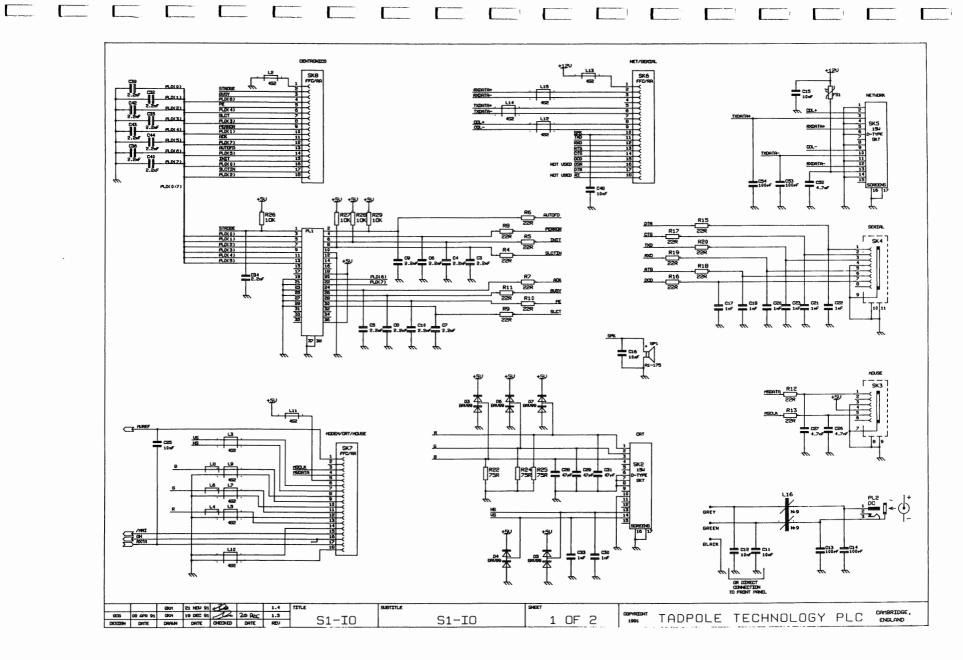

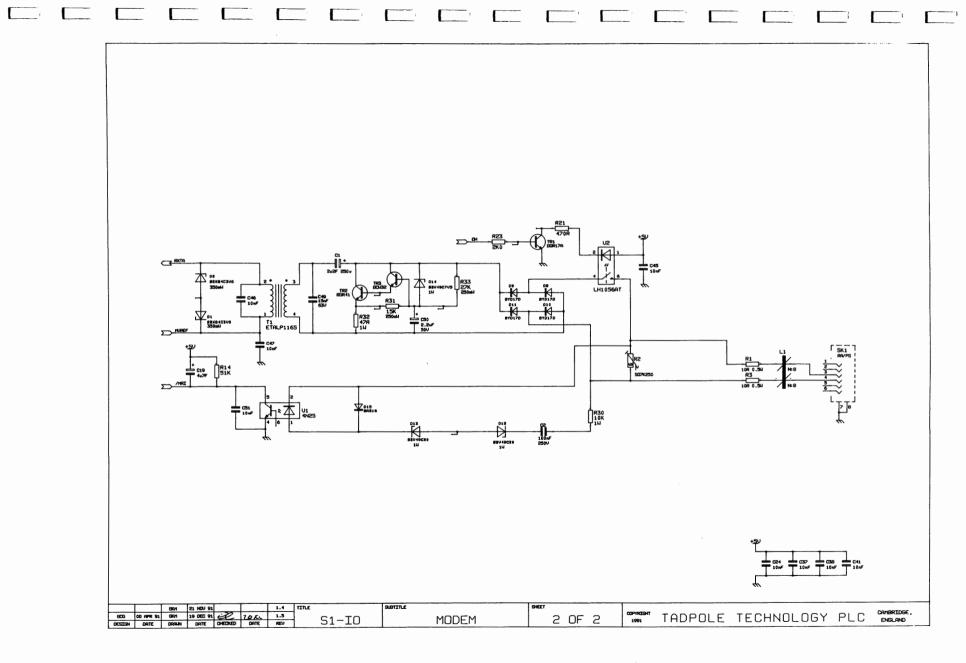

| S1-I/O SCHEMATIC DESCRIPTION                 |     |

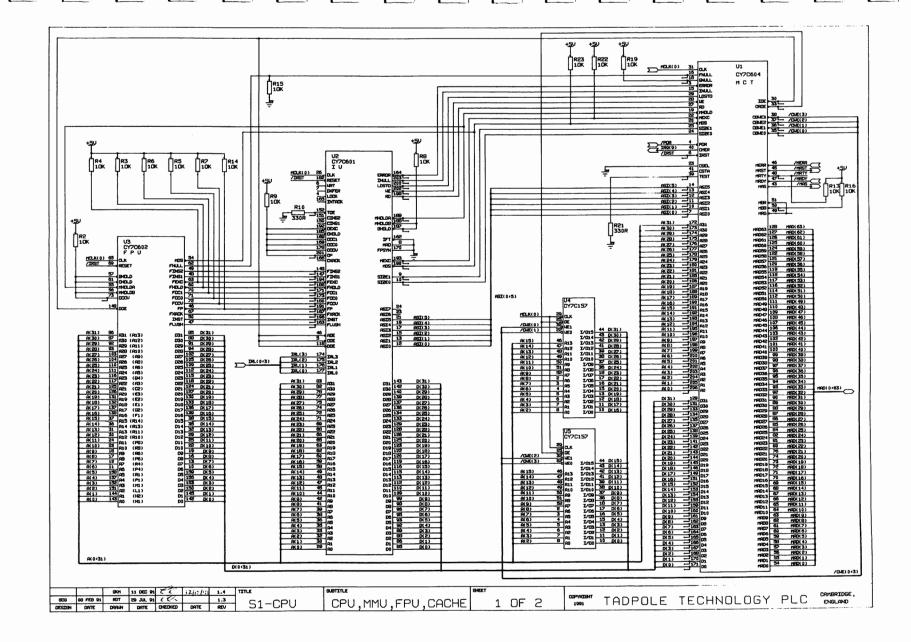

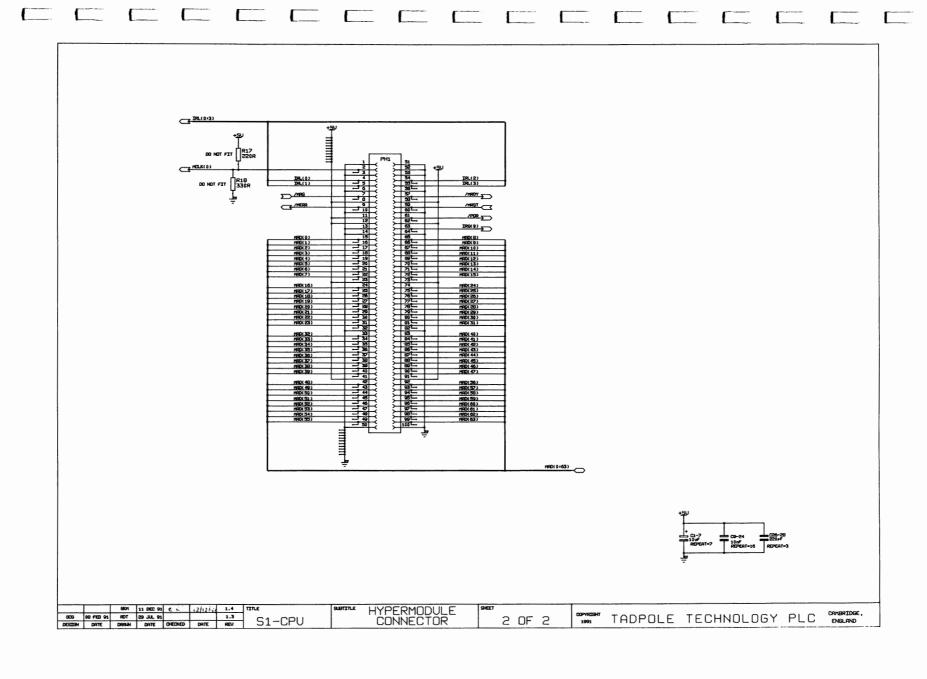

| S1-CPU SCHEMATIC DESCRIPTION                 | 149 |

| Sheet 1 - CY7C601 INTEGER UNIT               | 149 |

| Sheet 2 - 100-WAY MINIATURE CONNECTOR        | 149 |

| CILLA DEPUD MANAGERA                         |     |

| CHAPTER THIRTEEN                             |     |

| SYSTEM COMPONENT SPECIFICATIONS              |     |

| LCD COLOR DISPLAY                            |     |

| Mechanical Characteristics                   |     |

| Electrical Characteristics                   |     |

| Optical Characteristics                      |     |

| MONOCHROME DISPLAY                           |     |

| Mechanical Characteristics                   |     |

| Temperature Range                            |     |

| Absolute Maximum Ratings                     |     |

| Electrical Characteristics                   |     |

| Optical Characteristics                      |     |

| 80MBYTE HARD DISK                            |     |

| Mechanical Dimensions                        |     |

| Environmental limits                         |     |

| Power Requirements                           |     |

| Timing Specifications                        |     |

| 120MBYTE HARD DISK                           |     |

| Mechanical Dimensions                        |     |

| Environmental limits                         |     |

| Power Requirements                           |     |

| Timing Parameters                            | 161 |

# INTRODUCTION TO THE SPARCbook TECHNICAL REFERENCE MANUAL

The SPARCbook Technical Reference Manual is published as a supplement to the SPARCbook User's Guide to provide additional technical information. This document describes the hardware operation of the SPARCbook notebook computer and also provides details about the resident operating system supplied with each unit.

| MA | NU | AI. | STR | 110 | TI | IRE |

|----|----|-----|-----|-----|----|-----|

|    |    |     |     |     |    |     |

The SPARCbook Technical Reference Manual is structured as follows:

#### · Technical Overview

Chapter 1 discusses the principle features of the SPARCbook and introduces the reader to the main hardware devices that provide control over the SPARCbook's operations.

#### Architecture Overview

Chapter 2 describes the internal architecture of the SPARCbook, showing how the major devices are connected together.

#### Detailed Device Descriptions

Chapters 3 - 11 discuss in some depth the implementation of the major hardware devices in the SPARCbook.

#### Schematics Description

Chapter 12 provides a description of the schematic diagrams and discusses the theory of operation.

#### INTENDED AUDIENCE

The SPARCbook Technical Reference Manual is aimed at the hardware engineer wishing to carry out service or repairs, and at the software engineer wishing to implement hardware drivers.

It is assumed that the reader is familiar with the operation of SPARCbook, as detailed in the SPARCbook User Guide, and has a basic understanding of computer hardware.

## **CONVENTIONS USED IN THIS DOCUMENT**

The reader is advised to note the following conventions employed in the SPARCbook Technical Reference Manual.

### Logic states

The terms Clear or low indicate that the signal being discussed is at the logic level '0',

The terms Set or high indicate that the signal being discussed is at the logic level '1'.

The term Asserted indicates that a signal is in its true or active state regardless of whether that state is high or low.

The term *Negated* indicates that a signal is in its false or inactive state regardless of whether that state is high or low.

### **Data Length Definitions**

A Halfword is taken to contain 16 bits.

A word is taken to contain 32 bits.

A doubleword is taken to contain 64 bits

# CHAPTER ONE OVERVIEW

The SPARCbook provides in a compact notebook format many of the advanced features and high performance normally associated with desktop workstations. Low power consumption and compactness have been achieved by the use of highly integrated components without compromising either the functionality or performance of the SPARCbook.

The SPARCbook is housed in a magnesium alloy case measuring  $11.8" \times 8.5" \times 1.9"$ , and weighs 6.8lbs, including batteries and peripherals.

The SPARCbook's standard features include a 640 x 480 pixel color or monochrome liquid crystal display, an 82-key keyboard, a 3.5" floppy disk drive, an IDE hard disk drive, and Modem, Ethernet, Centronics and serial interfaces. A second hard disk drive is available as an option, when it is fitted in substitution for the floppy disk drive.

All of the major integrated circuit components are carried on a single printed circuit board, using the latest surface mount technology and avoiding the need for space consuming and power hungry expansion cards. The use of components with low power demand and the SPARCbook's advanced power management facilities allow the SPARCbook to be used continuously for 2.5 hours or more when powered from the battery.

#### **CENTRAL PROCESSOR**

Processing power in the SPARCbook is provided by the Cypress CY7C600 implementation of the Scalable Processor Architecture (SPARC) RISC microprocessor. The Cypress CY7C600 is a chip set which comprises the following:

- Integer Unit (IU)

- Cache Controller and Memory Management Unit (CMU)

- Optional Floating Point Unit (FPU)

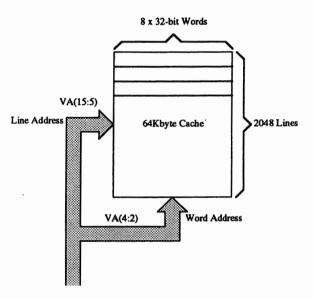

- 64Kbytes zero wait state Cache

The IU is the basic processing engine which executes all of the instruction set except for floating point instructions which are performed by the FPU when it is fitted. The CMU provides memory management and address translation facilities between the SPARC virtual bus and the main system bus. Two CY7C157 SRAM devices provide 64Kbytes of fast cache memory resident on the SPARC virtual bus.

The SPARC CPU is a RISC (reduced instruction set computer) based processor. It uses a simplified range of commands to carry out operations, enabling most instructions to execute within a single clock cycle.

Conventional processors tend to use large and complex instruction sets, taking several clock cycles to perform each instruction. Many of the instructions available to this type of processor are rarely if ever used, a fact that has led to the development of RISC processor concepts.

The already high performance of the SPARC CPU is further enhanced by the ability of FPU to execute instructions simultaneously with the IU, and by the provision of cache memory. The Cache memory is specialized area of fast (zero wait state) memory which allows many instructions and operands to be fetched locally by the CPU without it having to access the comparatively slow main memory.

#### **MAIN MEMORY**

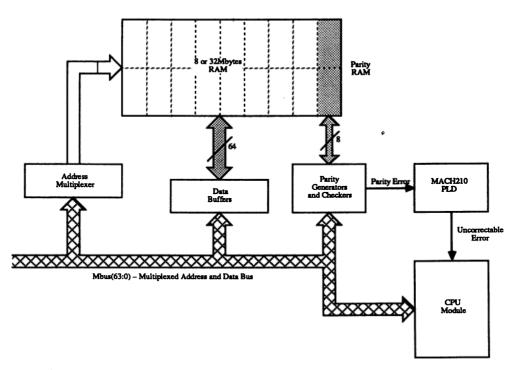

The SPARCbook is built using either 4Mbit or 16Mbit DRAM devices to provide 8 or 32Mbytes of DRAM. The main memory provides a 64-bit wide bus interface designed specifically to support burst cycles by the CPU.

The memory management unit maintains entries in cache memory called cache lines, each one a 256 bits wide copy of a similar sized area of main memory. When the IU requires data that is not present in the cache, the MMU copies the new data from main memory to cache memory using burst cycles of four 64-bit reads (see Chapter Three).

Using burst transfers, the memory interface is capable of a transfer rate of 72Mbyte/s. While using random access a transfer rate of 40Mbyte/s is achieved. Both rates are at a 25MHz processor clock speed.

The main memory also features software selectable parity protection.

#### **DISPLAY**

The SPARCbook is equipped with a 640 x 480 pixel color or monochrome liquid crystal flat panel display. Both types are side-lit by a cold fluorescent lamp, which can be controlled to vary the screen brightness. Reducing the brightness of the sidelight reduces the power consumption, prolonging battery life.

The display is controlled by a GD6410 VGA compatible display controller made by Cirrus Logic. This provides control for a monochrome LCD display and for an external color CRT display. Both displays may be used simultaneously. Advanced grey scale control by the GD6410 provides quality grey scale rendering of color images for clear display on the LCD.

In the color SPARCbook, a GD6340 color LCD controller provides the additional control required for the color LCD display. The color model is able to display 16 colors simultaneously from a palette of 262144.

The SPARCbook supports three display modes:

- Mode 1 Inbuilt LCD only

- Mode 2 Simultaneous LCD and standard VGA 640 x 480 Color monitor

- Mode 3 Extended VGA 800 x 600 external high resolution only

Both color and monochrome models of the SPARCbook are able to display an image in 16 colors on the external monitor. They are both able to display the same image simultaneously on the LCD and external CRT when in mode 2.

Mode 3 allows the SPARCbook to display an image on an external high resolution monitor, but turns the inbuilt LCD screen off. This mode requires the use of a multisync monitor.

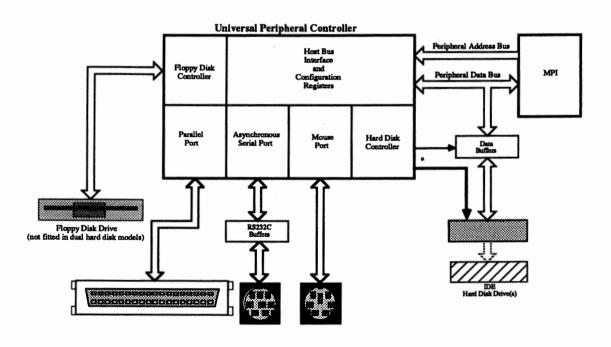

#### UNIVERSAL PERIPHERAL CONTROLLER

One of the highly integrated devices used in the SPARCbook to achieve its compact size is the 82C710 Universal Peripheral Controller (UPC) manufactured by Chips and Technologies Inc. This single device provides the following:

- · Hard Disk Control

- Floppy Disk Control

- Centronics Interfacing

- · External Mouse/Keyboard Interfacing

- RS232 Serial Interfacing

#### Floppy Disk Control

The UPC provides control for one or two IDE (Integrated Drive Electronics) PC/AT compatible hard disk drives. It provides a complete electronic interface, and control of a 16-bit data buffer.

#### Floppy Disk Control

Single hard disk versions of the SPARCbook contain a 3.5" floppy disk drive. The UPC provides an NEC765 compatible command set for control of the drive, and the SPARCbook's operating system allows 720Kbyte and 1.4Mbyte SUN and DOS format disks to be read and written.

#### **Centronics Interface**

The UPC provides control and data buffering for the parallel interface which appears on the rear panel of the SPARCbook. This interface supports connection to a printer with a Centronics interface.

#### **External Mouse/Kevboard Interface**

The UPC provides data buffering and control over a serial interface. This interface supports the connection of an external mouse or keyboard and appears via a 6-way mini DIN socket on the rear panel. This interface operates with TTL signal levels and does not allow the connection of RS232 devices.

#### **RS232 Serial Interface**

In addition to the TTL serial interface, the UPC provides data buffering and control over an RS232 serial interface.

| MICROCONTROLLER SUBSYSTEM | MI | CRC | CON | <b>ITROI</b> | I.F.R | SUR | SYSTEA |

|---------------------------|----|-----|-----|--------------|-------|-----|--------|

|---------------------------|----|-----|-----|--------------|-------|-----|--------|

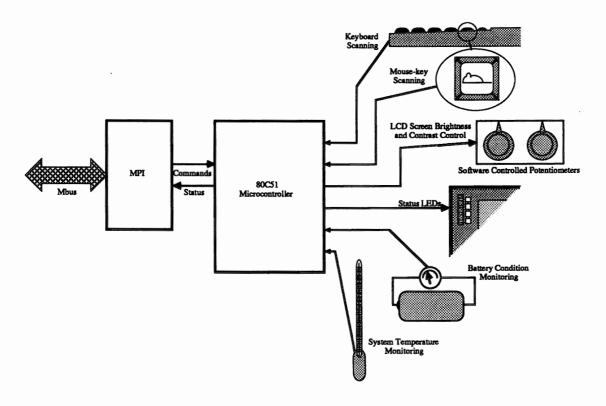

An 87C51 microcontroller provides control over the in-built keyboard, the bit I/O interface and the power management functions.

The bit I/O interface enables aspects of the SPARCbook's functionality to be controlled in software using keyboard commands. The microcontroller interprets certain special characters from the keyboard as being commands, and carries out system configuration changes accordingly. This includes display screen brightness and contrast.

The bit I/O interface also controls the LEDs next to the display in order to convey machine status information to the user.

The power management function maintains a constant check on the condition of the supply voltages, and provides early warning when the battery requires recharging. Recharging is carried an in-built power supply unit and battery charger when the SPARCbook is connected to an external electricity supply.

The microcontroller also provides control over the Mousekey.

#### ETHERNET INTERFACE

The SPARCbook is equipped with an IEEE802.3 compliant Ethernet interface controlled by a 86960 Network Interface Controller with Encoder (NICE) from Fujitsu. This provides complete control over the network interface.

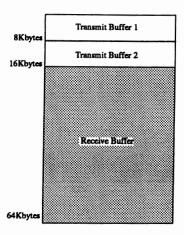

The NICE has direct control over a 64Kbyte area of SRAM in which it maintains receive and transmit buffers. The host is able write data into the transmit buffer and read data of the receive buffer via port in the NICE's address space. The NICE is able to carry out network operations with minimal demand on the CPU, and an integral driver and receiver interfaces directly to the 15-way D-type socket at the rear of the unit.

| MO      | ח   | F  | 1/ |

|---------|-----|----|----|

| IVI C I | 'IJ | r. | vi |

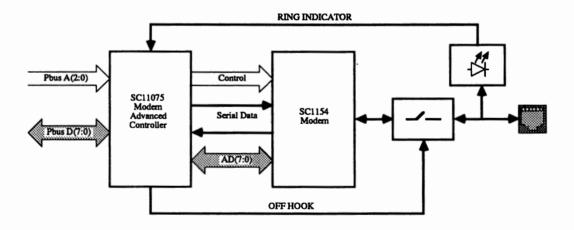

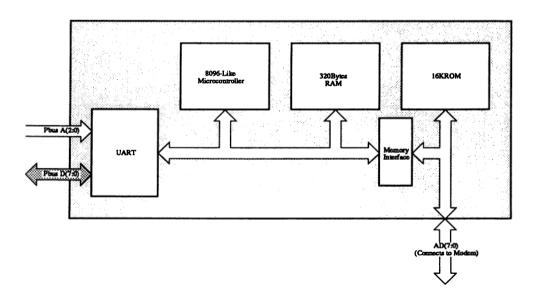

The SPARCbook's modem interface is implemented with chipset comprising a Sierra SC11075 Modem Access Controller (MAC) and SC11054. The SC11075 provides a direct interface between the host system and SC11054 modem; it incorporates an Intel 8096 equivalent processor core, supporting an AT command set; it contains a built-in 16C450 equivalent UART; and it contains 16Kbytes of on-chip ROM and 320bytes of RAM.

The SC11054 is a complete 2400bps (bits per second) modem IC which, when combined with the SC11075, provides Sendfax capability up to 9600bps.

The modem interface can be controlled completely using Hayes compatible commands written to the UART section of the MAC. Commands are sent to the interface using character strings, and these are interpreted by the MAC's in-built processor core and acted on appropriately.

Command characters and data for transmission onto the telephone line are written into the UART's transmit buffer. Data received from the telephone line and status information from the MAC can be read from the UART's receive buffer.

## REAL TIME CLOCK AND EPROM

Many of the background operations of the SPARCbook, such as system startup and battery condition monitoring, are controlled by the Tadpole resident firmware monitor. This is a body of software (most often referred to as firmware) that is permanently stored in an EPROM and is not erased when the machine is without power.

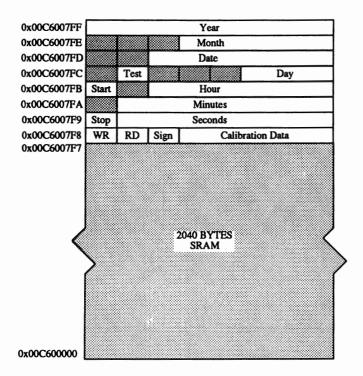

A 48T02 provides a battery backed real time clock and non-volatile RAM. This provides time of day clock and calendar functions and a 2Kbyte area of RAM which retains data when the board is without power.

A 1Mbit serially accessed EEPROM is used by the resident firmware to store the SPARCbook's Ethernet address and manufacturing information. The EEPROM is accessible via the microcontroller.

#### SPARCbook TECHNICAL SPECIFICATION

**Processor and Memory**

Processor 25MHz CY601 Integer Unit

Cache Controller/MMU 25MHz CY604 CMU

Cache 64Kbyte direct mapped virtual cache

FPU (optional) 25MHz CY602 Floating Point Unit

DRAM (standard) 8Mbytes with byte parity DRAM (-E models) 32Mbytes with byte parity

Components

**EPROM** 128Kbytes - 1Mbyte One 8-bit 32-pin JEDEC socket

**SERIAL** UPC One asynchronous RS232 port

TxD, RxD, CTS, RTS, DCD,

DTR, DSR, RING

MISC MK48T02 RTC/2Kbyte DRAM with battery backup

NMC93C46 1Kbit EEPROM

NETWORK Fujitsu NICE Controller IEEE802.3 interface with local buffer memory

DISK 82C710 UPC Controller Two IDE disks supported

Floppy disk controller

I/O Interfaces

Ethernet IEEE802.3 compliant

15-pin D-type AUI interface with slidelock

Centronics IBM PS/2 compatible interface

36-pin miniature D-type with cable to 25-pin

D-type socket

Mouse/Keyboard IBM PS/2 compatible (TTL)

6-pin mini-DIN socket

Modem 2400baud data and 9600baud SendFax

FCC Part 68 compliant, 0.3 REN V.29, V.27ter, V.22bis, V.22, V.21

Bell 212A, Bell 103 standards

RJ11 jack socket

VGA 640x480 25.057MHz dot clock

800x600 36.242MHz dot clock (external monitor)

15-pin PS/2 compatible D-type connector

Serial 110 to 38400baud

9-pin mini-DIN connector

Peripherals

Winchester disk 85Mbyte formatted IDE interface or 125Mbyte

formatted IDE interface, depending upon model

One or two drives per system

Maximum transfer rate 8Mbyte/s buffer to memory

Maximum sustained transfer rate 1.8Mbyte/s

Floppy disk 720Kbyte/1.44Mbyte formatted 3.5" floppy disk

drive

Fitted in single Winchester disk models

Display

Monochrome 640x480 VGA paper-white display side-lit

Displays 16 gray scales from 64

Color (-C models) 640x480 VGA color STN display side-lit

Displays 16 colors from 256

Keyboard

82-key notebook style with integral Mousekey

based upon Force Sensitive Resistor (FSR) tech-

nology

LEDs

External DC supply connected

Hard disk active

User controlled indicator

Battery low/exhausted indicator

Case and Emissions

Magnesium alloy AZ91 castings

SPARCbook is certified to FCC Part 15 Class B

· Power Supply

Internal Switched mode PSU with battery charge and

charge detection

facilities

External Universal input 110V-240V AC

Output 18V 0-3.1A DC

Physical

Dimensions 11.8" x 8.5" x 1.95"

Weight (with battery) 6.8lb/7.0lb (monochrome/color)

(without battery) 5.2lb/5.4lb (monochrome/color)

Environmental

Temperature (operational) 5-40 degrees Celsius

(storage) -20 - 60 degrees Celsius

Vibration (operational) 5-100Hz 0.25G

(storage) 5-100Hz 1.2G

Shock (operating) 4G

(storage) 50G

Humidity (operating) 8-80% relative humidity

Operating System

SunSoft Solaris 1.01 SPARCbook Version A

Comprising SunOS 4.1.2 sun4m architecture

OpenWindows V3

SPARCbook utilities

Meets SPARC Compliance Definition (SCD) 1.1

#### SPARCbook DETAILED ADDRESS MAP

This section provides a detailed address map for the SPARCbook. Please note the meanings of the following abbreviations used in the address map. All addresses are shown in hexadecimal.

R/W: R = read, W = Write

SIZE: b = byte, h= halfword (16-bits), w= word (32-bits), d = doubleword (64-bits)

| DRAM                  |                                                                |     | -       |

|-----------------------|----------------------------------------------------------------|-----|---------|

| ADDRESS               | DEVICE or REGISTER                                             | R/W | SIZE    |

| 000000000 - 0007FFFFF | DRAM (8Mbyte)                                                  | R/W | b/h/w/d |

| 000000000 - 001FFFFFF | DRAM (32Mbyte)                                                 | R/W | b/h/w/d |

| Display Controller    |                                                                |     |         |

| 00C000000 - 00CCFFFFF | CL-GD6410/CL-GD6340+ ceillys logic<br>CRTC Index MP 5/0/623-83 | 100 |         |

| 00C0003B4             | CRTC Index MP 5 (0/623-0)                                      | R/W | b       |

| 00C0003B5             | CRTC Data MP                                                   | R/W | b       |

| 00C0003C0             | Attribute Controller Index                                     | R/W | b       |

|                       | Data                                                           | W   | b       |

| 00C0003C1             | Attribute Controller Data                                      | R   | b       |

| 00C0003C2             | Misc Output                                                    | W   | b       |

|                       | Feature                                                        | R   | b       |

| 00C0003C3             | Motherboard Sleep Address                                      | R/W | b       |

| 00C0003C4             | Sequencer                                                      | R/W | b       |

| 00C0003C5             | Sequencer                                                      | R/W | ь       |

| 00C0003C6             | RAMDAC Pixel Mask                                              | R/W | ь       |

| 00C0003C7             | RAMDAC Address - Read Mode                                     | W   | b       |

|                       | RAMDAC Status Register                                         | R   | b       |

| 00C0003C8             | RAMDAC Address - Write Mode                                    | W   | ь       |

| 00C0003C9             | RAMDAC Data                                                    | R/W | b       |

| 00C0003CA             | Feature Control                                                | R   | b       |

| 00C0003CC             | Misc Output                                                    | R   | b       |

| 00C0003CE             | Graphics Controller and Extensions Index                       | R/W | b       |

| 00C0003CF             | Graphics Controller and Extensions Data                        | R/W | b       |

| 00C0003D4             | CRTC Index                                                     | R/W | b       |

| 00C0003D5             | CRTC Data                                                      | R/W | b       |

| 00C0003DA             | Feature Control                                                | W   | b       |

|                       | Display Status                                                 | R   | b       |

| 00C0046E8             | AT Adapter Sleep Address                                       | R/W |         |

Note † CL-GD6340 only present in color models. It contains RAMDAC registers shadow mapped over similar CL-GD6410 registers.

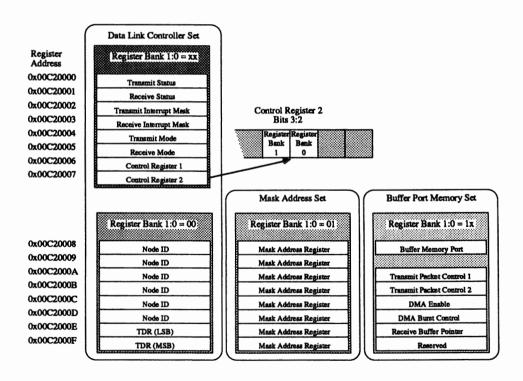

# **Ethernet Controller**

| 200000000000000000000000000000000000000 |                                             |     |      |

|-----------------------------------------|---------------------------------------------|-----|------|

| ADDRESS                                 | DEVICE or REGISTER                          | R/W | SIZE |

| 00C200000 - 00CFFFFF                    | Fujitsu 86960 NICE                          |     |      |

| 00C200000                               | Transmit Status                             | R/W | b    |

| 00C200001                               | Receive Status                              | R/W | b    |

| 00C200002                               | Transmit Interrupt Mask                     | R/W | b    |

| 00C200003                               | Receive Interrupt Mask                      | R/W | b    |

| 00C200004                               | Transmit Mode                               | R/W | b    |

| 00C200005                               | Receive Mode                                | R/W | ь    |

| 00C200006                               | Control Register 1                          | R/W | ь    |

| 00C200007                               | Control Register 2                          | R/W | ь    |

| 00C200008                               | Node ID (Register Bank 0)                   | R/W | ь    |

|                                         | Mask Address (Register Bank 1)              | R/W | ь    |

|                                         | Buffer Memory Port (Register Bank 2)        | R/W | h    |

| 00C200009                               | Node ID (Register Bank 0)                   | R/W | b    |

|                                         | Mask Address (Register Bank 1)              | R/W | ь    |

| 00C20000A                               | Node ID (Register Bank 0)                   | R/W | b    |

|                                         | Mask Address (Register Bank 1)              | R/W | b    |

|                                         | Transmit packet Control 1 (Register Bank 2) | R/W | b    |

| 00C20000B                               | Node ID (Register Bank 0)                   | R/W | b    |

|                                         | Mask Address (Register Bank 1)              | R/W | ь    |

|                                         | Transmit packet Control 2 (Register Bank 2) | R/W | ь    |

| 00C20000C                               | Node ID (Register Bank 0)                   | R/W | b    |

|                                         | Mask Address (Register Bank 1)              | R/W | ь    |

|                                         | DMA Enable (Register Bank 2)                | R/W | b    |

| 00C20000D                               | Node ID (Register Bank 0)                   | R/W | b    |

|                                         | Mask Address (Register Bank 1)              | R/W | Ъ    |

|                                         | DMA Burst Control (Register Bank 2)         | R/W | b    |

| 00C20000E                               | TDR (LSB) (Register Bank 0)                 | R/W | ь    |

|                                         | Mask Address (Register Bank 1)              | R/W | ь    |

|                                         | Receive Buffer Pointer (Register Bank 2)    | R/W | b    |

| 00C20000F                               | TDR (MSB) (Register Bank 0)                 | R/W | b    |

|                                         | Mask Address (Register Bank 1)              | R/W | ь    |

|                                         |                                             |     |      |

Note: Register Bank 0, 1 and 2 are selected using bits 2 and 3 of Control Register 2

| ADDRESS                                                                                                                       | DEVICE or REGISTER                                                 | R/W                                           | SIZE                  |

|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------|-----------------------|

| 00C400000 - 00C4FFFFF                                                                                                         | Sierra SC11075 – UART Registers                                    |                                               |                       |

| 00C400000                                                                                                                     | Receive Buffer                                                     | R                                             | b                     |

|                                                                                                                               | Transmit Buffer                                                    | W                                             | ь                     |

|                                                                                                                               | Divisor Latch (LSB)†                                               | R/W                                           | b                     |

| 00C400001                                                                                                                     | Interrupt Enable                                                   | R/W                                           | b                     |

|                                                                                                                               | Divisor Latch (MSB) †                                              | R/W                                           | b                     |

| 00C400002                                                                                                                     | Interrupt ID                                                       | R                                             | b                     |

| 00C400003                                                                                                                     | Line Control                                                       | R/W                                           | b                     |

| 00C400004                                                                                                                     | Modem Control                                                      | R/W                                           | ь                     |

| 00C400005                                                                                                                     | Line Status                                                        | R/W                                           | ь                     |

| 00C400006                                                                                                                     | Modem Status                                                       | R/W                                           | b                     |

| 00C400007                                                                                                                     | Scratch Pad                                                        | R/W                                           | b                     |

| Real Time Clock / SRAM                                                                                                        |                                                                    |                                               |                       |

|                                                                                                                               |                                                                    |                                               |                       |

| 00C600000 - 00C7FFFF                                                                                                          | MK48T02                                                            |                                               |                       |

| 00C600000 - 00C7FFFFF<br>00C600000                                                                                            |                                                                    | R/W                                           | b/h/w/                |

| 00C600000 - 00C7FFFFF<br>00C600000<br>00C6007F8                                                                               | MK48T02                                                            | R/W                                           | b/h/w/o               |

| 00C600000 - 00C7FFFFF<br>00C600000<br>00C6007F8<br>00C6007F9                                                                  | MK48T02<br>SRAM                                                    | R/W<br>R/W                                    | -,,                   |

| 00C600000 - 00C7FFFFF<br>00C600000<br>00C6007F8<br>00C6007F9<br>00C6007FA                                                     | MK48T02<br>SRAM<br>Calibration                                     | R/W<br>R/W<br>R/W                             | b                     |

| 00C600000 - 00C7FFFFF<br>00C600000<br>00C6007F8<br>00C6007F9                                                                  | MK48T02<br>SRAM<br>Calibration<br>Seconds                          | R/W<br>R/W                                    | b<br>b                |

| 00C600000 - 00C7FFFFF<br>00C600000<br>00C6007F8<br>00C6007F9<br>00C6007FA                                                     | MK48T02 SRAM Calibration Seconds Minutes                           | R/W<br>R/W<br>R/W                             | b<br>b<br>b           |

| 00C600000 - 00C7FFFFF<br>00C600000<br>00C6007F8<br>00C6007F9<br>00C6007FA<br>00C6007FB<br>00C6007FC<br>00C6007FD              | MK48T02 SRAM Calibration Seconds Minutes Hours                     | R/W<br>R/W<br>R/W<br>R/W                      | ь<br>ь<br>ь<br>ь      |

| 00C600000 - 00C7FFFFF<br>00C600000<br>00C6007F8<br>00C6007F9<br>00C6007FA<br>00C6007FB<br>00C6007FC<br>00C6007FD<br>00C6007FD | MK48T02 SRAM Calibration Seconds Minutes Hours Day                 | R/W<br>R/W<br>R/W<br>R/W<br>R/W               | b<br>b<br>b<br>b      |

| 00C600000 - 00C7FFFFF<br>00C600000<br>00C6007F8<br>00C6007F9<br>00C6007FA<br>00C6007FB<br>00C6007FC<br>00C6007FD              | MK48T02 SRAM Calibration Seconds Minutes Hours Day Date            | R/W<br>R/W<br>R/W<br>R/W<br>R/W               | b<br>b<br>b<br>b<br>b |

| 00C600000<br>00C6007F8<br>00C6007F9<br>00C6007FA<br>00C6007FB<br>00C6007FC<br>00C6007FD<br>00C6007FE                          | MK48T02 SRAM Calibration Seconds Minutes Hours Day Date Month Year | R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W        | b<br>b<br>b<br>b<br>b |

| 00C600000 - 00C7FFFFF 00C600000 00C6007F8 00C6007FA 00C6007FB 00C6007FC 00C6007FD 00C6007FE 00C6007FF                         | MK48T02 SRAM Calibration Seconds Minutes Hours Day Date Month Year | R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W | b<br>b<br>b<br>b      |

| 00C600000 - 00C7FFFFF 00C600000 00C6007F8 00C6007FA 00C6007FB 00C6007FC 00C6007FD 00C6007FE 00C6007FF                         | MK48T02 SRAM Calibration Seconds Minutes Hours Day Date Month Year | R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W        | b b b b b b b         |

# 8-Bit I/O Region – UPC Associated Interfaces

|                       | 15500tatou 17110tjuces                |     |      |

|-----------------------|---------------------------------------|-----|------|

| ADDRESS               | DEVICE or REGISTER                    | R/W | SIZE |

| 00CC00000 - 00CEFFFFF | 82C710 Universal Perpheral Controller |     |      |

| 00CC001F1             | IDE – Error Register                  | R   | ъ    |

| 00CC001F2             | IDE - Sector Count                    | R/W | ь    |

| 00CC001F3             | IDE - Sector Number                   | R/W | b    |

| 00CC001F4             | IDE – Cylinder Low                    | R/W | ъ    |

| 00CC001F5             | IDE – Cylinder High                   | R/W | ь    |

| 00CC001F6             | IDE - Drive/Head Register             | R/W | Ъ    |

| 00CC001F7             | IDE – Status Register                 | R   | ь    |

|                       | IDE - Command Register                | W   | ь    |

| 00CC003F6             | IDE - Alternate Status                | R   | ь    |

|                       | IDE – Fixed Disk Register             | W   | ь    |

| 00CC00310             | Mouse Port - Data Register            | R/W | ь    |

| 00CC00311             | Mouse Port - Status/Control Register  | R/W | b    |

| 00CC00330             | Parallel Port – Data Register         | R/W | ь    |

| 00CC00331             | Parallel Port - Status Register       | R   | ь    |

| 00CC00332             | Parallel Port - Command Register      | W   | ь    |

| 00CC00390             | UPC Configuration Index               | W   | ь    |

| 00CC00391             | UPC Configuration data                | R/W | ь    |

| 00CC003F2             | Floppy I/F – Digital O/P Register     | w   | ь    |

| 00CC003F4             | Floppy I/F - Main Satus Register      | R   | b    |

| 00CC003F5             | Floppy I/F - Data Register            | R/W | ь    |

| 00CC003F7             | Floppy I/F - Data Rate                | W   | Ъ    |

|                       | Floppy I/F - Digital Input Register   | R   | ь    |

| 00CC003F8             | UART – Receive Buffe                  | R   | ь    |

|                       | UART - Transmit Buffer                | W   | b    |

|                       | UART - Baud Rate Divisor (LSB)†       | R/W | b    |

| 00CC003F9             | UART – Interrupt Enable Register      | R/W | ъ    |

|                       | UART - Baud Rate Divisor (MSB)†       | R/W | b    |

| 00CC003FA             | UART - Interrupt Flag Register        | R/W | b    |

| 00CC003FB             | UART - Byte Format Register           | R/W | b    |

| 00CC003FC             | UART - Modem Control Register         | R/W | ъ    |

| 00CC003FD             | UART - Line Status Register           | R/W | ь    |

| 00CC003FE             | UART - Modem Status Register          | R/W | b    |

| 00CC003FF             | UART - Scratch Pad                    | R/W | ь    |

Note: † The Baud Rate Divisor Registers can only be accessed when bit 7 of the Byte Control Register is set.

# **MPI ASIC**

| ADDRESS             | DEVICE or REGISTER                | R/W  | SIZE |

|---------------------|-----------------------------------|------|------|

| 00D00000 - 00DFFFFF | Mbus to Pbus Interface Controller |      |      |

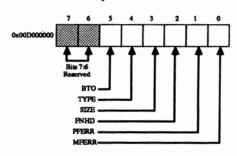

| 00D000000           | Mbus Error Status                 | R    | ь    |

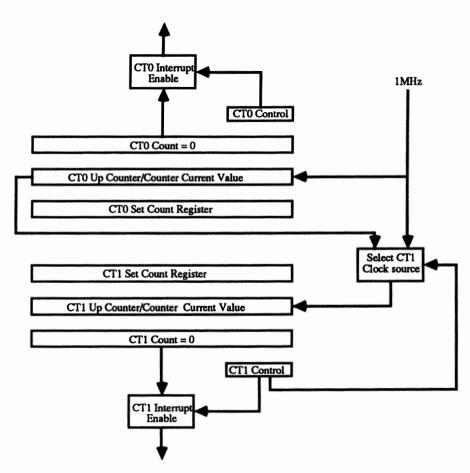

| 00D000010           | Set Count CT0                     | R/W  | w `  |

| 00D000018           | Current Count CT0                 | R    | w    |

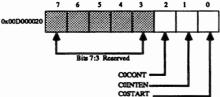

| 00D000020           | Control CT0                       | R/W  | ь    |

| 00D000028           | Set Count CT1                     | R/W  | w    |

| 00D000030           | Current Count CT1                 | R    | w    |

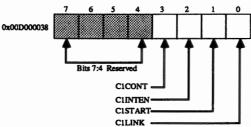

| 00D000038           | Control CT1                       | R/W  | ь    |

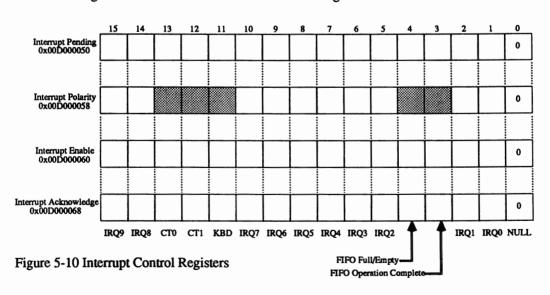

| 00D000050           | Interrupt Pending                 | R    | w    |

| 00D000058           | Interrupt Polarity                | R/W  | w    |

| 00D000060           | Interrupt Enable                  | R/W  | w    |

| 00D000068           | Interrupt Acknowledge             | W    | w    |

| 00D000070           | Serial Receive Port               | R    | b    |

| 00D000088           | Serial Receive Status             | R    | b    |

| 00D000090           | Serial Transmit Port              | W    | b    |

| 00D000098           | Serial Transmit Data              | W    | Ъ    |

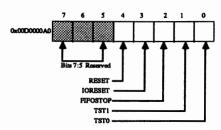

| 00D0000A0           | Reset                             | R/W  | b    |

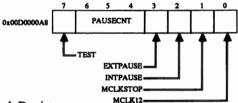

| 00D0000A8           | Clock Control                     | R/W  | b    |

| 00D0000B8           | Power Down                        | W    | b    |

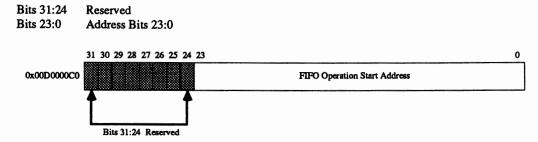

| 00D0000C0           | FIFO Start Address                | R./W | w    |

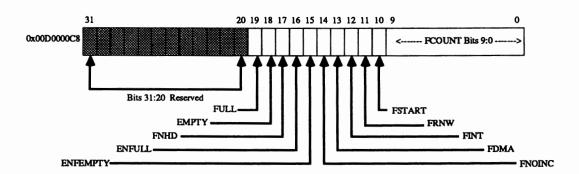

| 00D0000C8           | FIFO Control                      | R/W  | w    |

| 00D0000F8           | FIFO Data                         | R/W  | d    |

|                     |                                   |      |      |

R/W: R = read, W = Write

SIZE: b = byte, h = halfword (16-bits), w = word (32-bits), d = doubleword (64-bits)

# CHAPTER TWO ARCHITECTURE

One of the factors that contributes to the compactness of the SPARCbook is that at its heart is a single board of less than 12 square inches, the Base Board. This one board carries the processor module, provides 8 or 32Mbytes of memory and provides all of the control required for the display, keyboard, disks and interfaces.

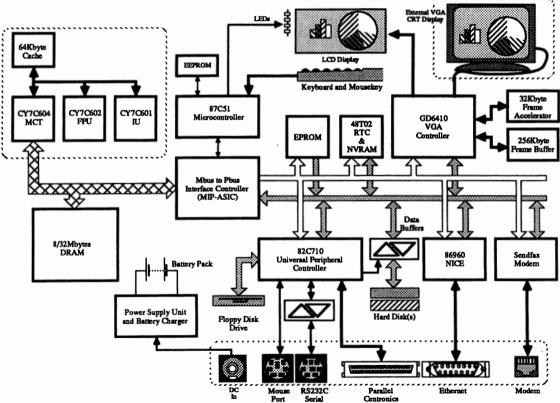

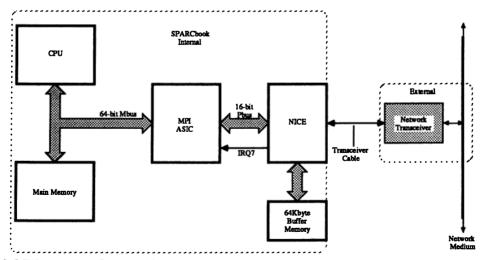

This section provides a brief description of the architecture of the SPARCbook. Figure 2-1 shows how the main components connect together.

Figure 2-1 SPARCbook Internal Architecture

#### **BUS STRUCTURE**

It will be seen from Figure 2-1 that the SPARCbook is based on a dual bus architecture, with the SPARC CPU and DRAM connected to a fast 64-bit bus, called the Mbus, and the I/O devices connected to a 16-bit peripheral bus called the Pbus.

The SPARC processor is the only Mbus master device and is able to access all locations in DRAM, and locations on the Pbus via the MPI.

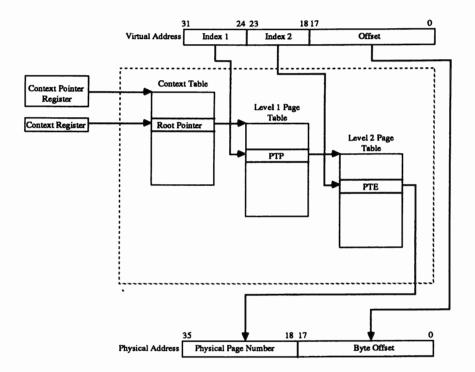

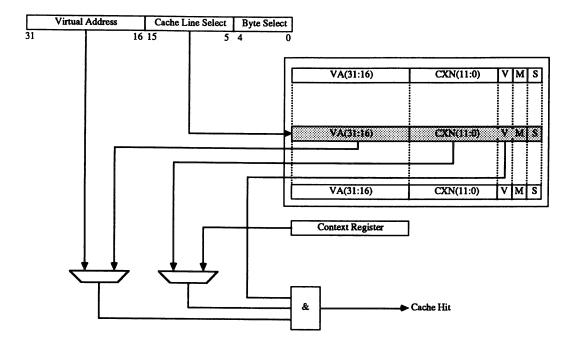

As described in the previous chapter, the SPARC CPU comprises the integer unit, floating point unit and the combined memory management unit and cache controller. These communicate via a private address bus which remains local to the SPARC chipset. This consists of a 32-bit address bus, an 8-bit address space identifier bus, and a 32-bit data bus. The IU uses logical (or virtual) addresses as labels to identify locations in its address space. The memory management unit translates the virtual addresses used on this bus into physical addresses used on the M-bus.

#### Mbus

The Mbus is an address and data multiplexed bus, which means that some of the wires are used to carry both address information and data, though at different times. The time when address information is on the bus is the address phase, and the time when data is on the bus is the data phase. In a SPARC based environment, a bus cycle consists of an address phase followed by one data phase for single access cycle, or an address phase and four data phases for a burst cycle.

The memory management unit produces a physical address on Mbus(35:0) and, during the address phase of the Mbus, provides bus control information on Mbus(45:36). The whole bus, Mbus(63:0), is used to transfer data during the data phase.

#### Pbus

The Pbus is a 16-bit PC-AT style bus which supports the on-board I/O devices. It consists of 16 data lines, PD(15:0), and 19 address lines, PA(18:0). The CPU addresses and exchanges data with the disk, Ethernet, modern and serial interfaces and the EPROM and RTC using the Pbus.

### Mbus - Pbus Interface

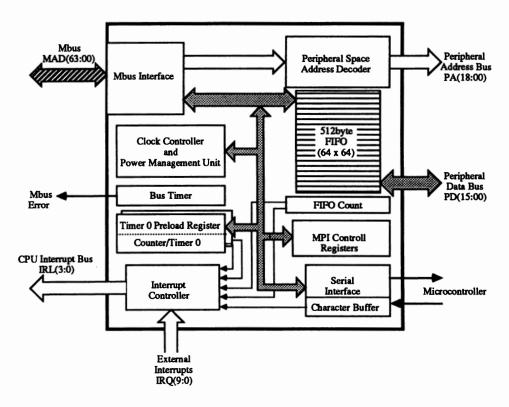

The gateway between the Mbus and Pbus is provided by the Mbus to Pbus Interface controller (MPI), a Tadpole Technology designed custom ASIC (Applications Specific Integrated Circuit).

The MPI provides an internal 512byte bidirectional FIFO, address decode facilities for the Pbus, interrupt support and two internal counter/timers. It provides a byte packing interface which converts between 8-, 16-, 32- and 64-bit accesses used on the Mbus, and 8- and 16-bit accesses used on the peripheral bus. This allows the two buses to operate at their optimum speed.

The MPI provides two data paths between the Mbus and Pbus.. The first path provides direct access by the CPU to the Pbus devices, and the second path is via the MPI's internal 512byte FIFO. The MPI also provides DMA support for floppy disk operations.

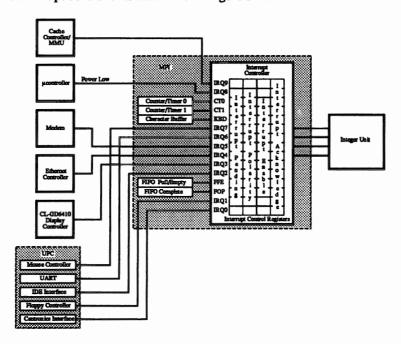

In addition to providing an interface between the Mbus and Pbus, the MPI contains a fifteen level interrupt controller and two 16-bit counter/timers. The interrupt controller section is used to consolidate the large number of interrupt requests from devices within the SPARCbook, and from the FIFO controller and counter/timers within the MPI. Interrupt controller provides the CPU with a code which identifies a pending interrupt, and allows individual interrupts to be masked

# CHAPTER THREE THE SPARC CPU MODULE

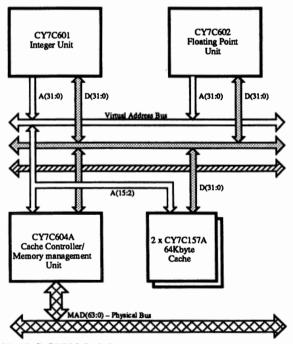

The SPARC CPU module comprises the CY7C601A integer unit (IU), the CY7C602A floating point unit (FPU), and the CY7C604A cache controller and memory management unit (CMU). In the SPARCbook implementation, these are carried on a small module along with two CY7C157A cache storage units (CSU).

The devices on the SPARCbook CPU module are connected together via a 32-bit virtual address bus and a 32-bit data bus. The CMU provides an interface between this bus and the Mbus. The Mbus is a SPARC architecture standard 64-bit multiplexed address and data bus that provides the SPARCbook with a high bandwidth data path between the CMU and main memory. The CMU performs address translations between these buses and provides memory management and cache control functions. The two CY7C157A SRAMs provide 64Kbytes of zero wait-state cache memory.

Figure 3-1 The SPARC CPU Module

#### CY7C601A INTEGER UNIT

The IU is the main processing engine that executes all of the instruction set except for floating point operations.

#### Instructions Overview

The CY7C600 architecture supports 62 integer instructions which fall into the following basic categories:

- Load and Store Instructions

- Arithmetic, Logical and Shift Instructions

- Control Transfer Instructions

- Read/Write Control Registers Instructions

The load and store instructions are the only instructions which cause the movement of data on the Mbus. They use two registers, or a register and a constant, to calculate the memory address involved. Halfword accesses must be aligned on 2-byte boundaries, word accesses on 4-byte boundaries, and doubleword accesses on 8-byte boundaries. These alignment restrictions greatly speed up memory access.

The arithmetic, logical and shift instructions compute a result that is a function of one or two source operands and then place the result non-destructively in a register. They perform arithmetic, logical, or shift operations.

The control transfer instruction category includes jumps, calls, traps, and branches. Control transfers are usually delayed until after execution of the next instructions so that the pipeline is not emptied every time a control transfer occurs, allowing compilers to be optimized for delayed branching.

The read/write control register instructions include instructions to read and write the contents of various control registers. Generally the source or destination is implied by the instructions.

In addition to the instruction types within the categories listed above, there are Floating Point instructions executed by the FPU.

Table 3-1 provides a summary of the IU instruction set.

| INPUTS                        | OPERATION                            |                           |

|-------------------------------|--------------------------------------|---------------------------|

| Load and Store Instructions   |                                      |                           |

| LDSB(LDSBA*)                  | Load Signed Byte                     | (from Alternate Space)    |

| LDSH(LDSHA*)                  | Load Signed Halfword                 | (from Alternate Space)    |

| LDUB(LDUBA*)                  | Load Unsigned Byte                   | (from Alternate Space)    |

| LDUH(LDUHA*)                  | Load Unsigned Halfword               | (from Alternate Space)    |

| LD(LDA*)                      | Load Word                            | (from Alternate Space)    |

| LDD(LDDA*)                    | Load Doubleword                      | (from Alternate Space)    |

| LDF                           | Load Floating Point                  | (arom reasonable of area) |

| LDDF                          | Load Double Floating Point           |                           |

| LDDFSR                        | Load Floating Point Status Register  |                           |

| LDC                           | Load Coprocessor                     |                           |

| LDDC                          | Load Double Coprocessor              |                           |

| LDDCSR                        | Load Coprocessor Status Register     |                           |

| STB(STBA*)                    | Store Byte                           | (In Alternate Space)      |

| STH(STHA*)                    | Store Halfword                       | (In Alternate Space)      |

| ST(STA*)                      | Store Word                           | (In Alternate Space)      |

| STD(STDA*)                    | Store Doubleword                     | (In Alternate Space)      |

| STF                           | Store Floating Point                 | (ar : areanane space)     |

| STDF                          | Store Double Floating Point          |                           |

| STFSR                         | Store Floating Point Status Register |                           |

| STDFQ*                        | Store Double Floating Point Queue    |                           |

| STC                           | Store Coprocessor                    |                           |

| STDC                          | Store Double Coprocessor             |                           |

| STCSR                         | Store Coprocessor Status Register    |                           |

| STDCO*                        | Store Double Coprocessor Queue       |                           |

| LDSTUB(LDSTUBA*)              | Atomic Load/Store Unsigned Byte      | (In Alternate Space)      |

| SWAP(SWAPA*)                  | Swap r Register With Memory          | (In Alternate Space)      |

| Arithmetic, Logical and Shift |                                      | •                         |

| ADD(ADDcc)                    | Add                                  | (Modify icc)              |

| ADDX(ADDXcc)                  | Add With Carry                       | (Modify icc)              |

| TADD(TADDccTV)                | Tagged Add and Modify icc            | (and Trap on Overflow)    |

| MULScc                        | Multiply Step and Modify icc         |                           |

| AND(ANDcc)                    | AND                                  | (Modify icc)              |

| ANDN(ANDNcc)                  | AND NOT                              | (Modify icc)              |

| OR(ORcc)                      | OR                                   | (Modify icc)              |

| ORN(ORNcc)                    | OR NOT                               | (Modify icc)              |

| XOR(XORcc)                    | Exclusive OR                         | (Modify icc)              |

| XNOR(XNORcc)                  | Exclusive NOR                        | (Modify icc)              |

| SLL                           | Shift Left Logical                   |                           |

| SRL                           | Shift Right Logical                  |                           |

| SRA                           | Shift Right Arithmetic               |                           |

| SETHI                         | Set High 22 Bits of r Register       |                           |

| SAVE                          | Save Caller's Window                 |                           |

| RESTORE                       | Restore Caller's Window              |                           |

| INPUTS                       | OPERATION                                |

|------------------------------|------------------------------------------|

| Control Transfer             |                                          |

| Bicc                         | Branch on Integer Condition Codes        |

| FBicc                        | Branch on Floating Point Condition Codes |

| CBccc                        | Branch on Coprocessor Condidition Codes  |

| CALL                         | Call                                     |

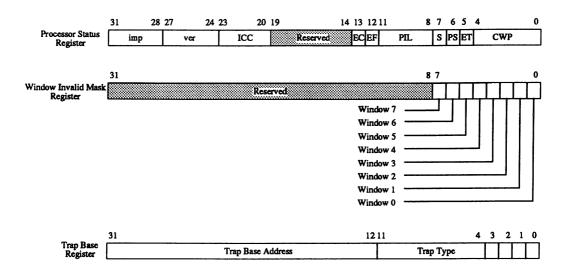

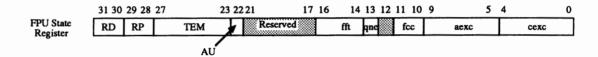

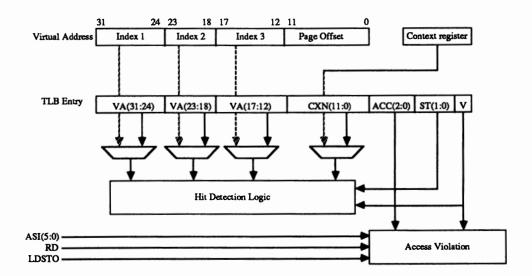

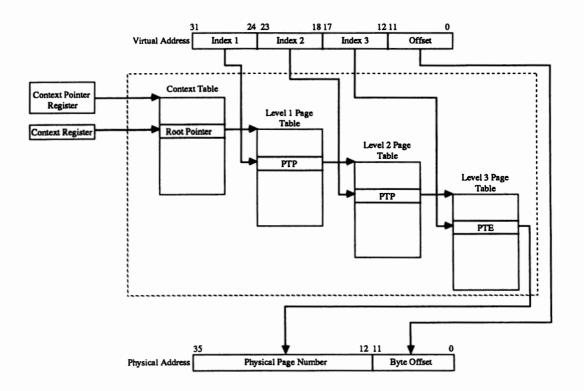

| JMPL                         | Jump and Link                            |