# Tru64 UNIX

# System Configuration Supplement: OEM Platforms

Part Number: AA-RJ1UA-TE

**July 1999**

Product Version: Tru64 UNIX Version 5.0 or higher

This manual provides information needed to set up OEM platforms running the Tru64 UNIX (formerly DIGITAL UNIX) operating system. It helps system and network administrators configure Alpha VME single-board computers (SBCs), PCI/ISA modular SBCs, and VMEbus backplane (vb) networks in which SBCs operate as Ethernet nodes.

#### © 1999 Compaq Computer Corporation

COMPAQ, the Compaq logo, and the Digital logo are registered in the U.S. Patent and Trademark Office.

Microsoft and Windows NT are registered trademarks of Microsoft Corporation. Intel, Pentium, and Intel Inside are registered trademarks of Intel Corporation. UNIX is a registered trademark and The Open Group is a trademark of The Open Group in the US and other countries. Other product names mentioned herein may be the trademarks of their respective companies.

Possession, use, or copying of the software described in this publication is authorized only pursuant to a valid written license from Compaq Computer Corporation or an authorized sublicensor.

Compaq Computer Corporation shall not be liable for technical or editorial errors or omissions contained herein. The information in this document is subject to change without notice.

# **Contents**

## **About This Manual**

| Platform Requirements and Restrictions                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Alpha VME 4/nnn and 5/nnn Single-Board Computers                    | 1–1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Verify CPU Version                                                  | 1–1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Firmware Requirements                                               | 1–2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Installing Tru64 UNIX                                               | 1–2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Configuring the VMEbus                                              | 1–2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Restrictions and Known Problems                                     | 1–2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1 VMEbus Autovectors Not Supported                                  | 1–2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2 Network Port Termination Required                                 | 1–2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3 Some TGA Video Card Configurations Require                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Disabling X Server DMA Writes                                       | 1–3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Writing VMEbus Device Drivers                                       | 1–4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PCI/ISA (DMCC) EBM2n and EBM4n Single-Board                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| •                                                                   | 1–4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Verify CPU Version                                                  | 1–5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Firmware Requirements                                               | 1–5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Installing Tru64 UNIX                                               | 1–5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Restrictions and Known Problems                                     | 1–5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1 Option Card Restrictions                                          | 1–6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PBXGB-AA (TGA2 PowerStorm 3D30) Video Card Restrictions             | 1–7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3 General Restrictions                                              | 1–8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Hardware Configuration for PCI/ISA (DMCC) 8-Headed Graphics Systems | 1–8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1 Hardware and Software Requirements                                | 1–8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2 Hardware Setup                                                    | 1–9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3 Software Setup                                                    | 1–10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| AXPvme Single-Board Computers                                       | 1–10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Firmware Upgrade Required                                           | 1–11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| · · · · · · · · · · · · · · · · · · ·                               | Alpha VME 4/nnn and 5/nnn Single-Board Computers Verify CPU Version Firmware Requirements Installing Tru64 UNIX Configuring the VMEbus Restrictions and Known Problems  1 VMEbus Autovectors Not Supported 2 Network Port Termination Required 3 Some TGA Video Card Configurations Require Disabling X Server DMA Writes Writing VMEbus Device Drivers PCI/ISA (DMCC) EBM2n and EBM4n Single-Board Computers Verify CPU Version Firmware Requirements Installing Tru64 UNIX Restrictions and Known Problems Option Card Restrictions PBXGB-AA (TGA2 PowerStorm 3D30) Video Card Restrictions General Restrictions Hardware Configuration for PCI/ISA (DMCC) 8-Headed Graphics Systems Hardware Setup AXPvme Single-Board Computers |

|   | 1.3.2    | Unpredictable Results When Performing Master Block Transfers | 1 |

|---|----------|--------------------------------------------------------------|---|

| 2 | Configur | ring the VMEbus for Alpha VME Systems                        |   |

|   | _        | MEbus Support Overview                                       |   |

|   |          | onfiguring VIP/VIC-Based Alpha VME SBCs                      |   |

|   | 2.2.1    | Configuring the vba_vipvic Subsystem                         |   |

|   | 2.2.1.1  | Specifying the VMEbus Request Level                          |   |

|   | 2.2.1.2  | Specifying the VIC Arbitration Mode                          |   |

|   | 2.2.1.3  | Specifying the VMEbus Fairness Timer Value                   |   |

|   | 2.2.1.4  | Specifying Bus Timeout Periods                               |   |

|   | 2.2.1.5  | Specifying the VMEbus Release Mode                           |   |

|   | 2.2.1.6  | Specifying System Controller VMEbus Resets                   |   |

|   | 2.2.1.7  | Special Considerations for VMEbus Resets                     |   |

|   | 2.2.1.8  | Specifying VMEbus Master Write Posting                       | 2 |

|   | 2.2.1.9  | Specifying the VMEbus DMA Interleave Gap                     | 2 |

|   | 2.2.1.10 | Specifying Limits on VMEbus DMA Reads                        | 2 |

|   | 2.2.1.11 | Specifying Limits on VMEbus DMA Writes                       | 2 |

|   | 2.2.1.12 | Specifying the DMA Method for SMP                            | 2 |

|   | 2.2.2    | Configuring VMEbus A32 and A24 Address Spaces                | 2 |

|   | 2.2.2.1  | Specifying A32 and A24 Address Space Overlapping.            | 2 |

|   | 2.2.2.2  | Configuring A32 and A24 Window Sizes                         | 2 |

|   | 2.2.2.3  | Specifying the A32 Base Address                              | 2 |

|   | 2.2.2.4  | Specifying the A24 Base Address                              | 2 |

|   | 2.2.3    | Configuring the VMEbus A16 Address Space                     | 2 |

|   | 2.2.4    | Configuring VMEbus Interrupts                                | 2 |

|   | 2.2.4.1  | VMEbus Interrupt Request Levels                              | 2 |

|   | 2.2.4.2  | Setting VMEbus Interrupt Vector Parameters                   | 2 |

|   | 2.2.4.3  | Specifying Autovector Interrupt Vectors                      | 2 |

|   | 2.2.4.4  | Specifying Module Switch Interrupt Vectors                   | 2 |

|   | 2.2.4.5  | Specifying Global Switch Interrupt Vectors                   | 2 |

|   | 2.2.5    | Using VMEbus Hardware Byte-Swapping Modes                    | 2 |

|   | 2.2.6    | Sharing Memory Between Big Endian and Little Endian          |   |

|   |          | Processors                                                   | 2 |

|   | 2.2.7    | Performing VMEbus Slave Block Transfers                      | 2 |

|   | 2.2.8    | Performing VMEbus Master Block Transfers with Local          | _ |

|   | 0001     | DMA                                                          | 2 |

|   | 2.2.8.1  | Routines for Master Block-Mode Transfers                     | 2 |

|   | 2.2.8.2  | Restrictions on VMEbus Master Block Transfers                | 2 |

|   | 2.2.9    | Using the Realtime Interrupt-Handling Routine                | _ |

|   |          | rt post callout                                              | 2 |

| 2.3      | Configuring UNIVERSE II-Based Alpha VME SBCs      | 2–28 |

|----------|---------------------------------------------------|------|

| 2.3.1    | Configuring the vba_univ Subsystem                | 2–29 |

| 2.3.1.1  | Specifying the Adapter Interrupt Dispatch Policy  | 2–37 |

| 2.3.1.2  | Specifying the Adapter PCI Scatter/Gather Maximum |      |

|          | Size                                              | 2–37 |

| 2.3.1.3  | Specifying the Adapter DMA Window Maximum Size    | 2–37 |

| 2.3.1.4  | Specifying the PCI Coupled Window Timer Value     | 2–38 |

| 2.3.1.5  | Specifying the PCI Maximum Retries                | 2–39 |

| 2.3.1.6  | Specifying the PCI Posted Write Transfer Count    | 2-39 |

| 2.3.1.7  | Specifying the PCI Aligned Burst Size             | 2-40 |

| 2.3.1.8  | Specifying the VMEbus Request Level               | 2-40 |

| 2.3.1.9  | Specifying the VMEbus Request Mode                | 2-40 |

| 2.3.1.10 | Specifying the VMEbus Release Mode                | 2-40 |

| 2.3.1.11 | Specifying the VMEbus Timeout Period              | 2-41 |

| 2.3.1.12 | Specifying the VMEbus Arbitration Mode            | 2-41 |

| 2.3.1.13 | Specifying the VMEbus Arbitration Timeout Period  | 2-41 |

| 2.3.1.14 | Specifying System Controller VMEbus Resets        | 2-42 |

| 2.3.1.15 | Special Considerations for VMEbus Resets          | 2-42 |

| 2.3.1.16 | Specifying the VMEbus On and Off Counters for     |      |

|          | MBLTs                                             | 2-44 |

| 2.3.2    | Configuring PCI-to-VME Address Spaces             | 2-44 |

| 2.3.2.1  | Enabling or Disabling a PCI-to-VME Window         | 2–47 |

| 2.3.2.2  | Specifying a PCI-to-VME Window VMEbus Base        |      |

|          | Address                                           | 2–47 |

| 2.3.2.3  | Specifying a PCI-to-VME Window Size               | 2–47 |

| 2.3.2.4  | Specifying PCI-to-VME Window VMEbus Address       |      |

|          | Modifiers                                         | 2–47 |

| 2.3.2.5  | Specifying a PCI-to-VME Window VMEbus Maximum     |      |

|          | Data Width                                        | 2–48 |

| 2.3.2.6  | Specifying PCI-to-VME Window Write Posting        | 2–48 |

| 2.3.2.7  | Specifying a PCI-to-VME Window VMEbus Cycle       |      |

|          | Type                                              | 2–49 |

| 2.3.3    | Configuring a Special A24/A16 PCI-to-VME Window   | 2–49 |

| 2.3.3.1  | Enabling or Disabling the A24/A16 Window          | 2–50 |

| 2.3.3.2  | Specifying A24/A16 Window Write Posting           | 2–51 |

| 2.3.3.3  | Specifying the A24/A16 Window VMEbus Maximum      |      |

|          | Data Width                                        | 2–51 |

| 2.3.4    | Configuring VME-to-PCI Address Spaces             | 2–51 |

| 2.3.4.1  | Enabling or Disabling a VME-to-PCI Window         | 2–53 |

| 2.3.4.2  | Specifying a VME-to-PCI Window VMEbus Base        |      |

|          | Address                                           | 2–53 |

|          |                                                   |      |

|   | 2.3.4.3  | Specifying a VME-to-PCI Window Size                 | 2–53 |

|---|----------|-----------------------------------------------------|------|

|   | 2.3.4.4  | Specifying VME-to-PCI Window VMEbus Address         | 0 50 |

|   | 2245     | Modifiers                                           | 2–53 |

|   | 2.3.4.5  | Specifying VME-to-PCI Window Write Posting          | 2–54 |

|   | 2.3.4.6  | Specifying VME-to-PCI Window Prefetch Reads         | 2–54 |

|   | 2.3.4.7  | Specifying VME-to-PCI Window 64-Bit PCI Bus         | 0 55 |

|   | 0.0.5    | Transactions                                        | 2–55 |

|   | 2.3.5    | Mapping UNIVERSE II CSRs to the VMEbus              | 2–55 |

|   | 2.3.5.1  | Enabling or Disabling the CSR Window                | 2–56 |

|   | 2.3.5.2  | Specifying a CSR Window VMEbus Base Address         | 2–56 |

|   | 2.3.5.3  | Specifying CSR Window VMEbus Address Modifiers .    | 2–56 |

|   | 2.3.6    | Mapping a Location Monitor Window to the VMEbus     | 2–57 |

|   | 2.3.6.1  | Enabling or Disabling the Location Monitor Window   | 2–58 |

|   | 2.3.6.2  | Specifying a Location Monitor Window VMEbus Base    |      |

|   |          | Address                                             | 2–58 |

|   | 2.3.6.3  | Specifying Location Monitor Window VMEbus           |      |

|   |          | Address Modifiers                                   | 2–58 |

|   | 2.3.7    | Configuring VMEbus Interrupts                       | 2–59 |

|   | 2.3.7.1  | VMEbus Interrupt Request Levels                     | 2–59 |

|   | 2.3.7.2  | Setting VMEbus Interrupt Vector Parameters          | 2–60 |

|   | 2.3.7.3  | Specifying Module Switch Interrupt Vectors          | 2–60 |

|   | 2.3.7.4  | Specifying Location Monitor Interrupt Vectors       | 2–62 |

|   | 2.3.8    | Using VMEbus Software Byte Swapping                 | 2-62 |

|   | 2.3.9    | Sharing Memory Between Big Endian and Little Endian |      |

|   |          | Processors                                          | 2-63 |

|   | 2.3.10   | Performing VMEbus Slave Block Transfers             | 2-63 |

|   | 2.3.11   | Performing VMEbus Master Block Transfers with Local |      |

|   |          | DMA                                                 | 2-64 |

|   | 2.3.11.1 | Routines for Master Block-Mode Transfers            | 2-64 |

|   | 2.3.11.2 | Restriction on VMEbus Master Block Transfers        | 2-66 |

|   | 2.3.12   | Using the Realtime Interrupt-Handling Routine       |      |

|   |          | rt_post_callout                                     | 2–66 |

| 3 | Configur | ing a VMEbus Backplane (vb) Network                 |      |

|   | 3.1 V    | MEbus Backplane (vb) Network Overview               | 3–2  |

|   | 3.1.1    | VMEbus Addresses Used for Client Communication      | 3–3  |

|   | 3.1.2    | VMEbus Addresses Used for Interrupting              | 3–4  |

|   | 3.1.3    | Box Manager Node                                    | 3–5  |

|   | 3.1.4    | Network Participation                               | 3–7  |

|   |          | onfiguring vb Network Nodes                         | 3–8  |

|   | 3.2 Co   | lodifying vb Driver Attributes                      | 3–9  |

|   | 5.5 IVI  | tourying vi Direct Attributes                       | 5–9  |

|   |          |                                                     |      |

| 3     | 3.3.1  | Modifying Per-Node vb Attributes              | 3–11 |

|-------|--------|-----------------------------------------------|------|

| 3     | 3.3.2  | Modifying Per-Network vb Attributes           | 3–15 |

| 3     | 3.4    | Modifying vba_vipvic Adapter Attributes       | 3–16 |

| 3     | 3.5    | Modifying vba_univ Adapter Attributes         | 3–18 |

| 3     | 3.6    | VIP/VIC Two-Node Network Example              | 3–19 |

| 3     | 3.7    | UNIVERSE II Two-Node Network Example          | 3-23 |

| 3     | 3.8    | Related ioctl Commands                        | 3-30 |

| 3     | 3.9    | Diagnostic Messages                           | 3–31 |

| 3     | 3.10   | Errors                                        | 3-32 |

| (     | 3.10.1 | System Startup Error Messages                 | 3-32 |

| :     | 3.10.2 | Post-Startup Error Messages                   | 3–32 |

| Inde  | x      |                                               |      |

| Table | es     |                                               |      |

| •     | 1–1    | Supported PCI/ISA Backplanes                  | 1–6  |

| •     | 1–2    | PCI/ISA Options Supported Behind the Bridge   | 1–7  |

| 2     | 2–1    | VIP/VIC VMEbus Adapter Defaults               | 2–4  |

| 2     | 2–2    | VIP/VIC VMEbus Interrupt Initial Defaults     | 2–5  |

| 2     | 2–3    | VIP/VIC VMEbus Interrupt Request Levels       | 2–18 |

| 2     | 2–4    | UNIVERSE II VMEbus Adapter Defaults           | 2-30 |

| 2     | 2–5    | UNIVERSE II VMEbus Interrupt Initial Defaults | 2-36 |

| 2     | 2–6    | UNIVERSE II VMEbus Interrupt Request Levels   | 2-59 |

| 3     | 3–1    | VIP/VIC VMEbus Address Space Defaults         | 3–17 |

## **About This Manual**

This manual provides information needed to set up OEM platforms running the  $Tru64^{TM}$   $UNIX^{\circledR}$  (formerly DIGITAL UNIX) operating system. It helps system and network administrators configure Alpha VME single-board computers (SBCs), PCI/ISA modular SBCs, and VMEbus backplane (vb) networks in which SBCs operate as Ethernet nodes.

#### **Audience**

This manual is for experienced system and network administrators who are thoroughly familiar with their platform's I/O bus and with the operating system concepts, commands, and configurations.

# Organization

This manual contains the following chapters.

Chapter 1 OEM Platform Requirements and Restrictions

Provides notes about the use of OEM platforms, with a section

devoted to each platform family.

Chapter 2 Configuring the VMEbus for Alpha VME Systems

Explains how to configure VMEbus adapters for OEM platforms,

with a section devoted to each major adapter type.

Chapter 3 Configuring a VMEbus Backplane (vb) Network

Explains how to set up a VMEbus backplane-based network in which Alpha VME single-board computers (SBCs) operate as

Ethernet nodes.

#### **Related Documents**

The following documents are relevant to setting up OEM platforms:

- System Configuration and Tuning

- System Administration

- Network Administration

- · Your platform's hardware documentation

- The sys attrs vba vipvic(7) kernel subsystem reference page

- The sys attrs vba univ(7) kernel subsystem reference page

- The sys attrs vme vba(7) kernel subsystem reference page

- The sys attrs(5) reference page

- The sysconfigdb(8) reference page

- Release Notes Processor-Specific Notes

- Installation Guide platform-specific instructions for booting

- Guide to Realtime Programming

- Device Driver Kit manual Writing VMEbus Device Drivers

- Device Driver Kit manual Writing PCI Bus Device Drivers

- DMCC Order Configuration Guide

The printed version of the Tru64 UNIX documentation uses letter icons on the spines of the books to help specific audiences quickly find the books that meet their needs. (You can order the printed documentation from Compag.) The following list describes this convention:

- G Books for general users

- S Books for system and network administrators

- Р Books for programmers

- D Books for device driver writers

- R Books for reference page users

Some books in the documentation help meet the needs of several audiences. For example, the information in some system books is also used by programmers. Keep this in mind when searching for information on specific topics.

The *Documentation Overview* provides information on all of the books in the Tru64 UNIX documentation set.

#### Reader's Comments

Compaq welcomes any comments and suggestions you have on this and other  $Tru64\ UNIX\ manuals.$

You can send your comments in the following ways:

- Fax: 603-884-0120 Attn: UBPG Publications, ZKO3-3/Y32

- Internet electronic mail: readers comment@zk3.dec.com

A Reader's Comment form is located on your system in the following location:

/usr/doc/readers\_comment.txt

Mail:

Compaq Computer Corporation UBPG Publications Manager ZKO3-3/Y32 110 Spit Brook Road Nashua. NH 03062-9987

A Reader's Comment form is located in the back of each printed manual. The form is postage paid if you mail it in the United States.

Please include the following information along with your comments:

- The full title of the book and the order number. (The order number is printed on the title page of this book and on its back cover.)

- The section numbers and page numbers of the information on which you are commenting.

- The version of Tru64 UNIX that you are using.

- If known, the type of processor that is running the Tru64 UNIX software.

The Tru64 UNIX Publications group cannot respond to system problems or technical support inquiries. Please address technical questions to your local system vendor or to the appropriate Compaq technical support office. Information provided with the software media explains how to send problem reports to Compaq.

# **Conventions**

This manual uses the following conventions:

| %      | A percent sign represents the C shell system prompt.                                                                                                                                                              |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| #      | A number sign represents the default superuser prompt.                                                                                                                                                            |

| >>>    | Three right angle brackets represent the console subsystem prompt.                                                                                                                                                |

| % cat  | Boldface type in interactive examples indicates typed user input.                                                                                                                                                 |

| file   | Italic (slanted) type indicates variable values, placeholders, and routine argument names.                                                                                                                        |

| :      | A vertical ellipsis indicates that a portion of an example that would normally be present is not shown.                                                                                                           |

| cat(1) | A cross-reference to a reference page includes the appropriate section number in parentheses. For example, cat(1) indicates that you can find information on the cat command in Section 1 of the reference pages. |

# OEM Platform Requirements and Restrictions

This chapter provides notes about the use of OEM platforms, with a section devoted to each platform family:

- Alpha VME 4/nnn and 5/nnn single-board computers (Section 1.1)

- PCI/ISA (DMCC) EBM2n and EBM4n single-board computers (Section 1.2)

- AXPvme single-board computers (Section 1.3)

## 1.1 Alpha VME 4/nnn and 5/nnn Single-Board Computers

The Alpha VME 4/nnn and 5/nnn platforms are members of a family of VMEbus-based single-board computers (SBCs). The part numbers for these SBCs are EBV14-xx (Alpha VME 4/nnn) and EBV16-xx (Alpha VME 5/nnn).

Support for the VIP/VIC64 VMEbus adapter on the Alpha VME 4/nnn and 5/nnn SBCs is consistent with the support for this adapter on AXPvme SBCs and Alpha VME 2100 systems.

The following notes are specific to Alpha VME 4/nnn and 5/nnn SBCs.

#### 1.1.1 Verify CPU Version

The sizer utility identifies the Alpha VME 4/nnn and 5/nnn SBCs as Alpha VME 4/nnn or 5/nnn family members. The sizer -c command displays the following output for Alpha VME 4/224 and 4/288 SBCs:

```

sysname> sizer -c

cpu "DECALPHAVME_224"

```

The sizer -c command displays the following output for Alpha VME 5/352 and 5/480 SBCs:

```

sysname> sizer -c

cpu "DECALPHAVME_320"

```

#### 1.1.2 Firmware Requirements

Before installing the operating system, make sure that your system has the correct firmware version. The minimum firmware versions required are Version 1.2 or higher for an Alpha VME 4/224 or 4/288 SBC, and Version 1.0 or higher for an Alpha VME 5/352 or 5/480 SBC. If you have an earlier firmware version, update your firmware before installing the operating system software. For information on how to update your firmware, see the firmware documentation.

To determine the version of firmware on your system, enter the following command at the console firmware prompt:

>>> show version

#### 1.1.3 Installing Tru64 UNIX

For information about installing the operating system on an Alpha VME 4/nnn or 5/nnn SBC, see the Tru64 UNIX *Installation Guide*. The *Installation Guide* provides platform-specific instructions for booting.

#### 1.1.4 Configuring the VMEbus

For information about configuring the VMEbus for an Alpha VME SBC, see Chapter 2.

For information about setting up a VMEbus backplane–based network in which Alpha VME SBCs operate as Ethernet nodes, see Chapter 3.

#### 1.1.5 Restrictions and Known Problems

The following restrictions apply to Alpha VME 4/nnn and 5/nnn SBCs.

### 1.1.5.1 VMEbus Autovectors Not Supported

The Alpha VME 4/nnn and 5/nnn SBCs do not support VMEbus autovectors.

#### 1.1.5.2 Network Port Termination Required

An Alpha VME 4/nnn or 5/nnn SBC that has the network configured in an up state must have its external network connection properly terminated. If the network connection is unplugged or not properly terminated, then the network software will periodically time out and perform a network reset. This is normal for an unterminated Alpha VME system. However, it will cause high system latencies during the reset period, resulting in delays of

about 10 milliseconds, which can affect the realtime performance of the system.

Note that a loopback connector is not sufficient to terminate the network connection.

# 1.1.5.3 Some TGA Video Card Configurations Require Disabling X Server DMA Writes

To use TGA video cards in some Alpha VME configurations, you must disable X server direct memory access (DMA) write operations. This restriction applies to the following configurations:

- EBVXG (TGA) video cards on Alpha 4/nnn and 5/nnn SBCs; note that the EBVXG video card is always installed behind the PCI-to-PCI bridge (PPB)

- TGA8 and TGA24 video cards on Alpha 5/nnn SBCs

| Other Restricted Configurations                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------|

| The restriction also applies to some configurations of TGA2 video cards on PCI/ISA (DMCC) EBM2n and EBM4n SBCs, as described in Section 1.2.4.2. |

The general procedure for disabling X server DMA write operations is as follows:

1. Bring the system to single-user mode.

If you are able to use the shutdown command, execute the following command as superuser:

# /usr/sbin/shutdown +2 "Disabling graphics DMA writes"

If you cannot use the shutdown command (for example, if the X server on the video card is hung), you must halt your system by pressing the hardware halt button and then reboot your system to single-user mode by entering the following command:

>>> boot -fl s

2. Mount all local file systems.

After your system is in single-user mode, mount all of your local file systems by entering the following command:

- # bcheckrc

- 3. Change the directory to /usr/var/X11 by entering the following command:

- # cd /usr/var/X11

- 4. Save a copy of the Xserver.conf file by entering a command such as the following:

- # cp Xserver.conf Xserver.conf.old

- 5. Edit the Xserver.conf file to add the text -pn -ffbDoDMA 4 to the command line arguments section, as follows:

```

! you specify command line arguments here

args <

-pn -ffbDoDMA 4</pre>

```

6. Return the system to multiuser mode by executing the following command:

```

# init 3

```

With this change, the video card and X server will run correctly on the SBC in multiuser mode.

#### 1.1.6 Writing VMEbus Device Drivers

For information about writing VMEbus device drivers, refer to the Tru64 UNIX Device Driver Kit (DDK), which is orderable separately from the base operating system.

You can browse a subset of device driver writing materials in the Library section of the Compaq Tru64 UNIX web site.

| Note                                                           |  |

|----------------------------------------------------------------|--|

| The Library section of the Compaq Tru64 UNIX web site also     |  |

| provides the latest DDK technical updates. DDK customers       |  |

| should check for potential DDK technical updates whenever they |  |

| install a new version of the operating system                  |  |

# 1.2 PCI/ISA (DMCC) EBM2n and EBM4n Single-Board Computers

The PCI/ISA EBM2n and EBM4n single-board computers (SBCs) are members of a family of PCI/ISA-based modular computing components. (The PCI/ISA systems and components product family was formerly known as DIGITAL Modular Computing Components, or DMCC).

The EBM2n SBCs are PICMG-compliant processor cards based on the Compaq Alpha 21164 CPU. The EBM4n SBCs are PICMG-compliant processor cards based on the Compaq Alpha 21064A CPU.

The following notes are specific to EBM2n and EBM4n SBCs.

#### 1.2.1 Verify CPU Version

The sizer utility identifies EBM2n and EBM4n SBCs as EBM2n or EBM4n family members. The sizer -c command displays the following output for EBM2n SBCs:

```

sysname> sizer -c

cpu "DECEV56 PBP"

```

The sizer -c command displays the following output for EBM4n SBCs:

```

sysname> sizer -c

cpu "DECEV45 PBP"

```

#### 1.2.2 Firmware Requirements

Before installing the operating system, make sure that your system has the correct firmware version. The minimum firmware version required for EBM2n and EBM4n SBCs is Version 4.7 or higher. If you have an earlier firmware version, update your firmware before installing the operating system software. For information on how to update your firmware, see the firmware documentation.

To determine the version of firmware on your system, enter the following console firmware command at the prompt:

```

>>> show version

```

#### 1.2.3 Installing Tru64 UNIX

For information about installing the operating system on an EBM2n or EBM4n SBC, see the Tru64 UNIX *Installation Guide*. The *Installation Guide* provides platform-specific instructions for booting.

#### 1.2.4 Restrictions and Known Problems

The following restrictions and known problems apply to EBM2n and EBM4n SBCs.

#### 1.2.4.1 Option Card Restrictions

You can use the PCI/ISA EBM2n and EBM4n SBCs on PCI/ISA backplanes in the ETMXB-xx and ETMAB-xx family. Table 1-1 lists the currently supported PCI/ISA backplanes.

Table 1–1: Supported PCI/ISA Backplanes

| Part Number | Description of Backplane                                                     |

|-------------|------------------------------------------------------------------------------|

| ETMXB-BA    | 5-slot PICMG (2 PCI, 1 PCI/ISA, 1 ISA, 1 SBC)                                |

| ETMXB-AA    | 7-slot PICMG (2 PCI, 1 PCI/ISA, 3 ISA, 1 SBC) with onboard SCSI controller   |

| ETMXB-DA    | 7-slot PICMG (3 PCI, 1 PCI/ISA, 1 ISA, 2 SBC [1 SBC slot usable at a time])  |

| ETMXB-CA    | 10-slot PICMG (6 PCI, 1 PCI/ISA, 1 ISA, 2 SBC [1 SBC slot usable at a time]) |

| ETMXB-EA    | 10-slot PICMG (4 PCI/ISA, 4 ISA, 2 SBC [1 SBC slot usable at a time])        |

| ETMAB-AB    | 14-slot PICMG (7 PCI, 6 ISA, 1 SBC)                                          |

| ETMAB-BB    | 14-slot PICMG (10 PCI, 3 ISA, 1 SBC)                                         |

| ETMAB-AC    | 19-slot PICMG (10 PCI, 7 ISA, 2 SBC [1 SBC slot usable at a time])           |

| ETMAB-BC    | 19-slot PICMG (13 PCI, 4 ISA, 2 SBC [1 SBC slot usable at a time])           |

#### **Table Notes**

- All ETMXB-xx and ETMAB-xx backplanes, except the 5-slot ETMXB-BA and the 7-slot ETMXB-AA and ETMXB-DA, use PCI-to-PCI bridge (PPB) technology to provide both primary (in front of the bridge) and secondary (behind the PPB) slots. All ETMAB-xx backplanes are PCI Version 2.1 compliant.

- Only the ETMXB-AA contains an onboard SCSI controller. The other ETMXB-xx and ETMAB-xx backplanes require a SCSI option card.

The option cards shown in Table 1–2, in addition to working in front of the bridge, work behind the bridge. You can plug these cards into any available slot.

Table 1–2: PCI/ISA Options Supported Behind the Bridge

| Option Type | Part Number | Description                 |

|-------------|-------------|-----------------------------|

| Graphics    | SN-PBXGB-AA | TGA2 2MB PowerStorm 3D30    |

| SCSI        | KZPAA-AA    | PCI-SCSI host bus adapter   |

| SCSI        | SN-KZPBA-CA | PCI-SCSI Ultra Wide adapter |

| Network     | DE450-CA    | PCI NIC (TP, TW, AUI)       |

| Network     | DE500-BA    | PCI NIC (TP)                |

#### **Table Notes**

- The SN-PBXGB-AA (TGA2 PowerStorm 3D30) video card will work behind a bridge in multiple configurations if the first card is within the primary bus. For restrictions on jumper settings and X server DMA for the PowerStorm 3D30 card, see Section 1.2.4.2.

- When used with PCI/ISA EBM2n SBCs, the SN-KZPBA-CA (PCI-SCSI Ultra Wide adapter) requires the following console parameter to be set:

>>> set pci prefetch SMS

#### 1.2.4.2 PBXGB-AA (TGA2 PowerStorm 3D30) Video Card Restrictions

The following restrictions apply to the PBXGB-AA (TGA2 PowerStorm 3D30) video card (listed in Table 1-2):

- EV5 Alias jumper setting (EBM2n only) For EBM2n SBCs only, you must set the EV5 Alias jumper on the PowerStorm 3D30 card to On.

- VGAEN jumper settings

- Only one PowerStorm 3D30 card can have its VGAEN jumper set to On. This card must be positioned in a primary PCI slot for the SRM Console to be displayed. All other PowerStorm 3D30 cards must have their VGAEN jumpers set to Off but may be positioned in any PCI slot. For more information about the jumpers, see the PBXGB-AA/CA PCI Graphics Option Owner's Guide, provided with the card.

- X server DMA write operations must be disabled for some configurations Some configurations of PowerStorm 3D30 cards on EBM2n and EBM4n SBCs require that you disable X server direct memory access (DMA) write operations. Specifically, you must disable these operations if the

system contains multiple PowerStorm 3D30 cards, or if any PowerStorm 3D30 graphics card is installed behind the PCI-to-PCI bridge (PPB). Follow the same general procedure for disabling X server DMA write operations that is described in Section 1.1.5.3.

#### 1.2.4.3 General Restrictions

The operating system does not support the operator control panel or watchdog timer. These server management features are supported only in the hardware and firmware.

#### 1.2.5 Hardware Configuration for PCI/ISA (DMCC) 8-Headed **Graphics Systems**

This section describes how to configure a PCI/ISA (formerly DIGITAL Modular Computing Components, or DMCC) system to run 8-headed graphics under the Tru64 UNIX operating system.

You can configure PCI/ISA platforms that contain a EBM2n-AZ Alpha PICMG single-board computer (SBC) and multiple PowerStorm 3D30 graphics cards to run multiheaded graphics, controlling up to eight monitors at a time.

#### 1.2.5.1 Hardware and Software Requirements

Running 8-headed graphics requires the following:

- An EBM2n-AZ Alpha PICMG SBC and eight PowerStorm 3D30 graphics cards within a fully configured PCI/ISA system.

- A PCI/ISA backplane and enclosure with at least 10 PCI slots, 512 MB main memory, a Compag-qualified Ethernet card, and all the other storage and I/O options normally required for such a system. (See the DMCC Order Configuration Guide.)

- The SBC occupies an SBC slot and the graphics cards occupy eight PCI slots; as explained in Section 1.2.5.2, placement of the graphics cards is critical.

- You must be running Version 4.0E or higher of the operating system, and you must be running the latest DMCC SRM code from Version 5.2 or higher of the Firmware CD-ROM.

The following PCI/ISA system configuration has been qualified by Compaq for running 8-headed graphics under Tru64 UNIX:

PCI/ISA Alpha 21164/366 MHz SBC with 2 MB cache and Tru64 UNIX license (EBM21-AZ)

- 512 MB main memory (2 x EBXMA-HC, for a total of four 128 MB DIMMs)

- Desktop enclosure with 14-slot PICMG backplane: 10 PCI, 3 ISA, 1 SBC (ETM33-BD)

- Eight PowerStorm 3D30 graphics cards (8 x SN-PBXGB-AA)

- PCI Ethernet card (DE450-CA)

- PCI fast/narrow SCSI controller (KZPAA-AA)

- Mandatory or associated options such as floppy/hard/CD-ROM drives, cable kit for PICMG enclosure, and power cord

- Tru64 UNIX (formerly DIGITAL UNIX) Version 4.0E or higher

- DMCC SRM code from the Version 5.2 Firmware CD-ROM

#### 1.2.5.2 Hardware Setup

When you configure the PCI/ISA 15-slot platform for 8-headed graphics, placement of the graphics cards is critical.

The Compaq-qualified configuration described in Section 1.2.5.1 uses an ETM33-BD desktop enclosure with 14-slot backplane. Within that enclosure, the PCI option cards must be placed into PCI slots in top-to-bottom order as follows:

- Secondary 32-bit PCI bus connectors

- **KZPAA SCSI card**

- PowerStorm graphics card: SCREEN 2

- PowerStorm graphics card: SCREEN 3

- PowerStorm graphics card: SCREEN 4

- DE450 Ethernet card

- PowerStorm graphics card: SCREEN 5

- PowerStorm graphics card: SCREEN 6

- PowerStorm graphics card: SCREEN 7

- Primary 64-bit PCI bus connectors

- PowerStorm graphics card: SCREEN 0 (VGA ENABLED)

- PowerStorm graphics card: SCREEN 1

For reference, the power connector is situated above the PCI slots, and the SBC and ISA connectors are below.

All PowerStorm cards must have their Alias jumper IN and VGA EN jumper OUT, except the SCREEN 0 card, which must be VGA-enabled.

#### 1.2.5.3 Software Setup

After you complete hardware configuration for the 8-headed system, you can set up the operating system to operate the eight screens as one row of eight screens (8x1) or two rows of four screens (4x2).

By default in a multiheaded configuration, the screens are operated as 8x1. To set up the screens in a 4x2 combination, you must edit your system's X Window System server configuration file, /usr/var/X11/Xserver.conf.

Instructions for editing this file to customize the X server configuration are provided in the Xserver(1X) reference page.

To set up 4x2 operation, you need to specify -edge top, -edge bottom, -edge right, and -edge left command line arguments that arrange and attach the screens as you wish them. Each argument takes scr1 and scr2 values, which are the numbers of the screens you are attaching.

For example, you could arrange the eight screens as follows:

| 4 | 5 | 6 | 7 |

|---|---|---|---|

| 0 | 1 | 2 | 3 |

ZK-1559U-AI

To achieve this combination, add the appropriate command line arguments to the command line arguments section of Xserver.conf, as follows:

```

! you specify command line arguments here

args <

-pn

-edge_top0 4

-edge_top1 5 -edge_top2 6

-edge_top3 7

-edge_bottom4 0 -edge_bottom5 1 -edge_bottom6 2 -edge_bottom7 3 -edge_right0 1 -edge_right1 2 -edge_right2 3 -edge_right4 5 -edge_right5 6 -edge_right6 7

-edge left1 0 -edge left2 1 -edge left3 2 -edge left5 4 -edge_left6 5 -edge_left7 6

```

# 1.3 AXPvme Single-Board Computers

The following notes are specific to the AXPvme SBCs. The part numbers for these SBCs include EBV10-xx (AXPvme 100) and EBV12-xx (AXPvme 166 and 230).

#### 1.3.1 Firmware Upgrade Required

AXPvme SBCs must upgrade to Version 17.0 or higher of the AXPvme firmware to run the current version of the operating system.

# 1.3.2 Unpredictable Results When Performing Master Block Transfers

The following restriction applies to the VIP/VIC adapter used on AXPvme SBCs and Alpha VME 2100 systems. Performing master block transfers with a data width of D64 can produce unpredictable results in the following cases:

- If D64 slave access is performed before memory has been mapped to the VMEbus.

- If memory access does not coincide with the appropriate access mode, such as attempting user access to memory specified as supervisory-mode access.

- If the AXPvme SBC or Alpha VME 2100 system is a VMEbus interrupter and is targeted for D64 slave access. The interrupt vector presented by the VMEbus interrupter may not be the vector specified in the vba\_post\_irq routine.

Memory must be mapped to the VMEbus prior to D64 slave access. Access to memory must coincide with the appropriate access mode. If supervisory-mode access is specified when memory is mapped, memory accesses must use supervisory mode. If user-mode access is specified, both supervisory and user access are allowed.

See the Tru64 UNIX Device Driver Kit manual *Writing VMEbus Device Drivers* (available separately from the base operating system) for more information on slave and master block transfers.

# Configuring the VMEbus for Alpha VME Systems

This chapter explains how to configure the VMEbus for OEM platforms running Tru64 UNIX. The chapter provides an overview followed by sections that address groups of platforms based on their VMEbus adapter type:

- VMEbus support overview (Section 2.1)

- Configuring VIP/VIC-based Alpha VME SBCs (Section 2.2)

- Configuring UNIVERSE II-based Alpha VME SBCs (Section 2.3)

## 2.1 VMEbus Support Overview

The Tru64 UNIX operating system includes a generic VMEbus interface layer that provides customers with a consistent interface to VMEbus devices across Alpha workstation and server platforms and Alpha VME single-board computers (SBCs).

The operating system supports the following PCI/VMEbus adapters:

- UNIVERSE II PCI64-to-VME64 adapter

- VIP/VIC PCI32-to-VME64 adapter

- DWP64 PCI32-to-VME64 adapter

- DWPVC PCI32-to-VME32 adapter

Alpha VME SBCs provide an integrated PCI/VMEbus adapter: either VIP/VIC or UNIVERSE II. The DWP64 and DWPVC adapters are provided in layered product kits for use with Alpha workstation and server platforms.

For information about the VMEbus-based systems supported by the operating system, see the Tru64 UNIX Software Product Description (SPD).

This chapter provides information about configuring the VMEbus on the Alpha VME family of SBCs. To configure a VMEbus backplane (vb) network with Alpha VME SBCs in the same backplane communicating as network nodes, see Chapter 3.

To write VMEbus device drivers, you must obtain the Tru64 UNIX Device Driver Kit (DDK), which is available separately from the base operating system. The DDK provides a detailed VMEbus device driver example that you can run on the Alpha VME SBCs.

To write VMEbus device drivers for Alpha workstation and server platforms with DWP64 or DWPVC adapters, you must have the associated adapter driver software and documentation in addition to the DDK. Be sure to check for the required processor and hardware configurations. For more information about the DWP64 and DWPVC adapters, see the PCI32/VME64 Adapter Driver SPD and the PCI/VME Adapter Driver SPD.

### 2.2 Configuring VIP/VIC-Based Alpha VME SBCs

This section describes how to set up VIP/VIC-based Alpha VME systems for use on the VMEbus, including how to modify attributes of the vba vipvic kernel subsystem.

VMEbus setup allows you to run the operating system on the following VIP/VIC-based AXPvme and Alpha VME systems:

- AXPvme single-board computers (SBCs)

- Alpha VME 4/224 and 4/228 SBCs

- Alpha VME 5/352 and 5/480 SBCs

- Alpha VME 2100 system

For information about installing the operating system on the listed systems, see the Installation Guide.

For information about setting up UNIVERSE II-based Alpha VME systems for use on the VMEbus, see Section 2.3.

This section addresses the following topics relating to the use of the VMEbus on the listed systems:

- Configuring the vba vipvic subsystem (Section 2.2.1)

- Configuring VMEbus A32 and A24 address spaces (Section 2.2.2)

- Configuring the VMEbus A16 address space (Section 2.2.3)

- Configuring VMEbus interrupts (Section 2.2.4)

- Using VMEbus hardware byte-swapping modes (Section 2.2.5)

- Sharing memory between big endian and little endian processors (Section 2.2.6)

- Performing VMEbus slave block transfers (Section 2.2.7)

- Performing VMEbus master block transfers with local DMA (Section 2.2.8)

- Using the realtime interrupt-handling routine rt\_post\_callout (Section 2.2.9)

### 2.2.1 Configuring the vba\_vipvic Subsystem

This section describes how to configure the <code>vba\_vipvic</code> kernel subsystem in order to prepare VIP/VIC-based AXPvme and Alpha VME systems for use on the VMEbus.

You configure the VIP/VIC adapter by examining the default attributes supplied for the <code>vba\_vipvic</code> subsystem, determining which attributes (if any) you want to change, then modifying the <code>/etc/sysconfigtab</code> file on your machine. After modifying <code>/etc/sysconfigtab</code>, you must shut down and reboot the system.

| Note |  |

|------|--|

|------|--|

Do not directly edit /etc/sysconfigtab. Instead, use the sysconfigdb facility, as described in the sysconfigdb(8) reference page. It is recommended that you maintain private sysconfigtab file fragments for vba\_vipvic attributes and use sysconfigdb switches to add (-a -f), delete (-d), or merge (-m -f) vba\_vipvic attribute values. The example in Section 3.6 illustrates this approach. The sys\_attrs(5) reference page provides additional guidelines for editing kernel subsystem attributes. You must always reboot after changing vba\_vipvic subsystem attributes.

Common modifications to the vba\_vipvic subsystem default attributes are to reconfigure the A32, A24, and A16 address spaces. For example, you could use sysconfigdb to edit the following modifications into /etc/sysconfigtab:

```

vba_vipvic:

A32_Base = 0x10000000

A32_Size = 0x08000000

A24_Base = 0x00A00000

A24_Size = 0x200000

A16_Base = 0x000000000

```

In this example, the A24 inbound DMA window base address is modified from the default 0x00C00000 to 0x00A0000; the A24 window size from the default 4 MB to 2 MB; and the A16 interprocessor communication base address from the default 0x00000100 to 0x00000000.

You can modify values for the following VIP/VIC adapter attributes; each list item corresponds to a later subsection:

VMEbus request level (Section 2.2.1.1)

VIC arbitration mode (Section 2.2.1.2)

VMEbus fairness timer value (Section 2.2.1.3)

Local bus and VMEbus timeout periods (Section 2.2.1.4)

VMEbus release mode (Section 2.2.1.5)

System controller VMEbus resets (Section 2.2.1.6)

VIC master write posting (Section 2.2.1.8)

VMEbus DMA interleave gap (Section 2.2.1.9)

VMEbus DMA read limit (Section 2.2.1.10)

VMEbus DMA write limit (Section 2.2.1.11)

DMA method (hardware or emulated) for SMP systems

(Section 2.2.1.12)

You can also modify the following values for the A32, A24, and A16 address spaces that the VMEbus hardware architecture defines; each list item corresponds to a later subsection:

A32 and A24 overlapping address configuration (Section 2.2.2.1)

A32 and A24 DMA inbound window sizes (Section 2.2.2.2)

A32 DMA inbound window base address (Section 2.2.2.3)

A24 DMA inbound window base address (Section 2.2.2.4)

A16 base for interprocessor communication facilities (Section 2.2.3)

Table 2-1 lists the defaults supplied for various VMEbus parameters. The default values specified should provide proper VMEbus operation for most applications. Be careful when modifying these values; not all adapters support all fields.

Table 2-1: VIP/VIC VMEbus Adapter Defaults

| Parameter      | Default | Meaning                                      |

|----------------|---------|----------------------------------------------|

| VME_Br_Lev     | 0x03    | Bus request level 3 for master cycles        |

| VIC_Arb_Mode   | 0x00    | Arbitration mode is round robin              |

| VME_Fair_Req   | 0x00    | VMEbus fair requester disabled               |

| VIC_Loc_Bus_To | 0x05    | Local bus timeout period is 256 microseconds |

| VME_Bus_To     | 0x06    | VMEbus timeout period is 512 microseconds    |

| VIC_Rel_Mode   | 0       | Release mode is release on request (ROR)     |

Table 2–1: VIP/VIC VMEbus Adapter Defaults (cont.)

| Parameter      | Default    | Meaning                                                           |

|----------------|------------|-------------------------------------------------------------------|

| VIC_Syscon     | 1          | System controller VMEbus reset is enabled                         |

| VIC_Wrt_Post   | 0          | Disable VIC master write posting                                  |

| VIC_DMA_Intrlv | 15         | DMA interleave gap is 3.75 microseconds (value * 250 nanoseconds) |

| Lmt_DMA_Rd     | 0          | No DMA read limit                                                 |

| Lmt_DMA_Wrt    | 0          | No DMA write limit                                                |

| Frce_Hw_DMA    | 0          | Do not force hardware DMA engine on SMP systems                   |

| A32_Base       | 0x08000000 | A32 inbound DMA window base address                               |

| A32_Size       | 0x8000000  | A32 window size (128 MB)                                          |

| A24_Base       | 0x00C00000 | A24 inbound DMA window base address                               |

| A24_Size       | 0x400000   | A24 window size (4 MB)                                            |

| A16_Base       | 0x00000100 | A16 interprocessor communication base address                     |

| A16_Mask       | 0x00000000 | A16 interprocessor communication mask                             |

| A24_A32_Ovrlap | 1          | Inbound A24/A32, if same space, overlap                           |

Table 2–2 lists VMEbus interrupt parameters and their initial defaults. These defaults are later overwritten by system priority level (SPL) values supplied by the platform. See the values listed in Table 2-3, or query the values at run time using the command sysconfig -q vba vipvic.

Table 2-2: VIP/VIC VMEbus Interrupt Initial Defaults

| Parameter | Default | Meaning                            |

|-----------|---------|------------------------------------|

| Irq0_SPL  | 3       | VMEbus IRQ level to system SPL map |

| Irq1_SPL  | 3       | VMEbus IRQ 1 to SPL SPLDEVLOW      |

| Irq2_SPL  | 3       | VMEbus IRQ 2 to SPL SPLDEVLOW      |

| Irq3_SPL  | 3       | VMEbus IRQ 3 to SPL SPLDEVLOW      |

| Irq4_SPL  | 3       | VMEbus IRQ 4 to SPL SPLDEVLOW      |

| Irq5_SPL  | 3       | VMEbus IRQ 5 to SPL SPLDEVLOW      |

| Irq6_SPL  | 3       | VMEbus IRQ 6 to SPL SPLDEVLOW      |

| Irq7_SPL  | 3       | VMEbus IRQ 7 to SPL SPLDEVLOW      |

Table 2-2: VIP/VIC VMEbus Interrupt Initial Defaults (cont.)

| Parameter        | Default | Meaning                                    |

|------------------|---------|--------------------------------------------|

| Adapt_Blk_SPL    | 3       | Adapter resource blocking SPL<br>SPLDEVLOW |

| DMA_Access_Space | 0       | Adapter MBLT I/O access: sparse            |

#### 2.2.1.1 Specifying the VMEbus Request Level

You can specify one of the following values for the VMEbus request level (parameter VME Br lev). The value is stored in the VIC64 Arbiter/Requester Configuration Register (ARCR).

| 0x00 | VMEbus request level BR0           |

|------|------------------------------------|

| 0x01 | VMEbus request level BR1           |

| 0x02 | VMEbus request level BR2           |

| 0x03 | VMEbus request level BR3 (default) |

#### 2.2.1.2 Specifying the VIC Arbitration Mode

You can specify one of the following values for the VMEbus arbitration mode (parameter VIC Arb Mode). The VMEbus arbitration mode is stored in the VIC64 Arbiter/Requester Configuration Register (ARCR). This parameter is applicable only when the VMEbus adapter is configured to be the system controller.

| 0x00 | $VIC\ performs\ round\text{-}robin\ VMEbus\ arbitration\ (default)$ |

|------|---------------------------------------------------------------------|

| 0x01 | VIC performs priority VMEbus arbitration                            |

### 2.2.1.3 Specifying the VMEbus Fairness Timer Value

You can specify one of the following values for the Arbiter/Requester fair request timeout (parameter VME Fair Reg). The fair request timeout value is stored in the VIC64 Arbiter/Requester Configuration Register (ARCR).

| 0x00 | Fairness disabled (default)           |

|------|---------------------------------------|

| 0x01 | Fair request timeout = 2 microseconds |

| 0x02 | Fair request timeout = 4 microseconds |

| 0x03 | Fair request timeout = 6 microseconds |

| 0x04 | Fair request timeout = 8 microseconds |

| 0x05 | Fair request timeout = $10$ microseconds |

|------|------------------------------------------|

| 0x06 | Fair request timeout = 12 microseconds   |

| 0x07 | Fair request timeout = 14 microseconds   |

| 0x08 | Fair request timeout = 16 microseconds   |

| 0x09 | Fair request timeout = 18 microseconds   |

| 0x0A | Fair request timeout = 20 microseconds   |

| 0x0B | Fair request timeout = 22 microseconds   |

| 0x0C | Fair request timeout = 24 microseconds   |

| 0x0D | Fair request timeout = 26 microseconds   |

| 0x0E | Fair request timeout = 28 microseconds   |

| 0x0F | Fair request timeout = none              |

#### 2.2.1.4 Specifying Bus Timeout Periods

You can specify one of the following values for the local bus timeout period (parameter VIC Loc Bus To) and for the VMEbus timeout period (parameter VME\_Bus\_To). Each value is stored in the VIC64 Transfer Timeout Register (TTR). The local bus timeout period must be shorter than the VMEbus timeout period.

| 0x00 | Timeout = 4 microseconds                           |

|------|----------------------------------------------------|

| 0x01 | Timeout = 16 microseconds                          |

| 0x02 | Timeout = 32 microseconds                          |

| 0x03 | Timeout = 64 microseconds                          |

| 0x04 | Timeout = 128 microseconds                         |

| 0x05 | Timeout = 256 microseconds (default for local bus) |

| 0x06 | Timeout = 512 microseconds (default for VMEbus)    |

| 0v07 | Timeouts disabled                                  |

#### 2.2.1.5 Specifying the VMEbus Release Mode

You can specify one of the following values for the release mode (parameter VIC Rel Mode). The release-mode value is stored in the VIC64 Release Control Register (RCR).

- 0 Release on request (ROR) — the default

- 1 Release when done (RWD)

#### 2.2.1.6 Specifying System Controller VMEbus Resets

You can specify one of the following values to indicate whether or not the adapter should issue VMEbus resets if it is the system controller (parameter VIC Syscon).

For AXPvme SBCs and Alpha VME 4/nnn and 5/nnn SBCs, in addition to specifying a value from this list, you must set the configuration switches to indicate whether or not the SBC is the VMEbus system controller. See the SBC's installation guide for information on setting the module configuration switches.

The Alpha VME 2100 adapter is always the VMEbus system controller. There are no module configuration switches to disable it from being the system controller.

The VMEbus backplane must have only one system controller. The system controller must be electrically the first module in the VMEbus backplane and in most systems must be in the first VMEbus slot.

- Do not issue VMEbus resets if system controller 0

- Issue VMEbus resets if system controller (default)

The values specified interact with the VMEbus initialization code to determine whether a VMEbus reset is issued when the VMEbus adapter is being configured. If the value is set to 1 and the system being booted is the system controller, as determined by the VMEbus initialization code, a VMEbus reset is issued. If you do not want a VMEbus reset issued during VMEbus adapter configuration, set the value to 0 (zero). These values pertain only to the system controller.

If the system controller is configured to issue a VMEbus reset during adapter initialization, and other processor modules are installed in the VMEbus backplane, boot the system controller first to allow devices and processor modules to perform their bus reset actions.

#### 2.2.1.7 Special Considerations for VMEbus Resets

The system controller should always be the initiator of VMEbus resets. However, under certain error conditions, other VMEbus adapter modules may invoke a VMEbus reset. Modules installed in the VMEbus backplane react to bus resets differently. Some modules, if configured, perform a

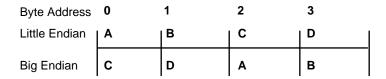

module reset. Some VMEbus adapters may have their VMEbus interface reset to a power-up state without notification to the operating system. This could leave the VMEbus adapter in an unconfigured state, cause unwanted effects to the operating system and its device drivers, and cause VMEbus errors to occur. Other VMEbus adapters on the VMEbus may accept VMEbus resets and attempt to reconfigure the VMEbus adapter to the hardware context it was running before the bus reset occurred. However, device drivers expecting interrupts may not receive them and I/O hardware operations may be canceled by the VMEbus reset without notification to the device driver. There is also a potential for data corruption to occur when the VMEbus adapter is reset during an I/O operation.