# Sun 3

# **Customer Maintenance**

**Training Manual**

(Revision H)

September 10, 1988

Sun Microsystems, Incorporated Educational Services Department

## **Credits and Trademarks**

Sun Workstation is a registered trademark of Sun Microsystems, Inc.

SunStation, Sun Microsystems, SunCore, SunWindows, SunOS, SunView, DVMA and the combination of Sun with a numeric suffix are registered trademarks of Sun Microsystems, Inc.

UNIX, UNIX/32V, UNIX System III and UNIX System V are trademarks of AT&T Bell Laboratories.

Intel and Multibus are registered trademarks of Intel Corporation.

Copyright 1988 by Sun Microsystems.

This publication is protected by Federal Copyright Law, with all rights reserved. No part of this publication may be reproduced, stored in a retrieval system, translated, transcribed, or transmitted, in any form, or by any means manual. electric, electronic, electro-magnetic, mechanical, chemical, optical or otherwise, without prior explicit written permission from Sun Microsystems.

### **REVISION HISTORY**

| REV LEVEL | DATE          | COMMENTS                                                                                                                                            |

|-----------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| A         | 01 June 1985  | First edition of this manual                                                                                                                        |

| В         | 28 Feb. 1986  | Second edition. Add 3/50 lowcost desktop<br>Greyscale display<br>Added to VME/MB                                                                    |

| С         | 15 Dec. 1986  | Third edition. Add 3/110<br>3/200<br>FPA<br>Enhanced TroubleShooting section                                                                        |

| D         | 15 Sept. 1987 | Fourth edition. Add 3/60 low cost desktop color.<br>New SCSI<br>Enhanced Diagnostic section<br>Enhanced Lab section<br>New peripherals descriptions |

| E         | 15 Dec. 1987  | Fifth edition. Add 3/150 6 slot chassis<br>New Lab Projects<br>General clean up                                                                     |

| F         | 10 Mar. 1988  | Sixth edition. Add ALM-2<br>Updated Lab Projects<br>Updated Options Section                                                                         |

| G         | 10 June 1988  | Seventh edition<br>Updated Lab Projects<br>Updated Options Section<br>Add GP2, CG5 and EXEC                                                         |

| н         | 10 Sept. 1988 | Eighth edition.<br>Updated Lab Projects,<br>Add TAAC-1, Channel Attach, 3E Reference                                                                |

### Sun–3 Customer Maintenance Training

#### Course Objectives and Overview

This course will prepare technical users and support engineers to perform all aspects of Sun3 maintenance to the Field Replaceable Unit (FRU) level. Students will install, configure and verify functionality of all existing Sun3 workstations. Malfunctions will be inserted into each functional area for troubleshooting using all available Sun3 diagnostics. Sun3 add-ons and upgrades will be installed and diagnosed during the class.

#### Course Format

The course is 5 days (9Am –5Pm) Instruction is a combination of lecture (40%) and guided hands–on lab with troubleshooting (60%).

#### Target Audience and Prerequisites

This course is designed for technical personnel responsible for installation, configuration, maintenance and upgrades of Sun3 workstations.

Sun Installation and Networking is a Prerequisite. Experience with digital computer architecture and system troubleshooting is assumed.

You are overqualified for this course if: You are able to install, configure, upgrade

and troubleshoot the entire product line of Sun3 workstations

You are underqualified for this course if: You have not taken the Sun Installation and Networking course.

#### Materials

Students receive a course manual with system and architecture block diagrams,

guided lab projects, theory of operations and configuration charts including all user selectable jumpers.

#### Overview of Topics

Sun3 products product description Sun3 Architecture (includes Motorola MC68020, MC68881) Installation and operation Configuration Power VME Bus operation SCSI Bus and device operation Video theory and operation Video theory and operation Diagnostics System Troubleshooting Upgrades and add-ons

•

#### Day 1

| Introduction<br>Course objectives, content and schedule<br>Sun3 Overview                            | (.5 hours)  |

|-----------------------------------------------------------------------------------------------------|-------------|

| Physical identification and capabilities                                                            | (1.5 hours) |

| System Block diagram<br>Device descriptions, Data flow, Control flow                                |             |

| MC68020, MC68881                                                                                    | (1 hour)    |

| VME Bus                                                                                             |             |

| Operation and error codes                                                                           | (.5 hours)  |

| SCSI Bus                                                                                            |             |

| Operation, device descriptions and error codes                                                      | (.5 hours)  |

| Lab                                                                                                 |             |

| Familiarization and booting procedures, physical identification of systems, verification of working |             |

| systems                                                                                             | (3 hours)   |

#### Day 2

| Configuration                                      |             |

|----------------------------------------------------|-------------|

| Board, device and cable placement                  |             |

| jumper and switch settings, power adjustments      | (3 hours)   |

| Lab                                                |             |

| Configure all boards, devices and switch settings. |             |

| perform power adjustments                          | (4.0 hours) |

Day 3

Sun Diagnostics

...

.

-

.

| How to load, run and interpret all Sun        |             |

|-----------------------------------------------|-------------|

| diagnostics and monitor commands              |             |

| (includes EEPROM)                             | (3.0 hours) |

| Lab                                           |             |

| Set up, run and interpret all Sun diagnostics |             |

| and monitor commands                          | (4.0 hours) |

## Day 4

•

| System troubleshooting Lab               |             |

|------------------------------------------|-------------|

| Isolate and repair inserted malfunctions | ı           |

| in each system area                      | (8.0 hours) |

## Day 5

.

| System add ons and upgrades                    |              |

|------------------------------------------------|--------------|

| Theory and installation procedures for upgrade | es such as · |

| graphics and Asynchronus Multi-Line            |              |

| Adapter (ALM)                                  | (3.0 hours)  |

| Lab                                            |              |

| Install and verify upgrades                    | (4.0 hours)  |

#### CHAPTER BREAKDOWN

- CHAPTER ONE: Sun 3 Architectural Overview

- II CHAPTER TWO: System Bus Operations

- III CHAPTER THREE: System Configuration

- IV CHAPTER FOUR: Diagnostics And Troubleshooting

- V CHAPTER FIVE: Using The EEPROM

- VI CHAPTER SIX: Display Characteristics

- VII CHAPTER SEVEN:

SECTION A- SCSI Card SECTION B- Color Card SECTION C- VME/MB Adapter SECTION D- Graphics Processor Card SECTION E- Graphics Buffer Card SECTION F- FPA Card SECTION F- FPA Card SECTION G- ALM-2 Terminal Interface Card SECTION H- GP2/CG5 SECTION I- TAAC-1 SECTION J- Channel Attach

- VIII CHAPTER EIGHT: 3/50 Low-End Desktop Workstation

- IX CHAPTER NINE: 3/110 Low Cost Color Workstation

- X CHAPTER TEN: 3/200 Series of High End Workstations

- XI CHAPTER ELEVEN: 3/60 One Slot Color Desktop

### TABLE OF CONTENTS

| CHAPTER ONE: SUN 3                               |

|--------------------------------------------------|

| ARCHITECTURAL OVERVIEW                           |

| Overview                                         |

| 1.1 68020 Microprocessor Overview                |

| 1.3 68020 Operations 1-4                         |

| 1.4 Virtual Memory Implementation                |

| 1.5 Space Organization on Sun 3 Architecture 1-6 |

| 1.6 Space Mapping 1-7                            |

| 1.7 Memory Management Unit(MMU) Overview 1-8     |

| 1.8 Physical Address Map                         |

| 1.81 CPU Devices 1–12                            |

| 1.9 Device and Control Data Path                 |

| 1.11 Control Devices on the TTL Bus 1-15         |

| 1.12 ID PROM                                     |

| 1.13 System Enable Register                      |

| 1.14 User DVMA Enable Register                   |

| 1.15 Bus Error Register                          |

| 1.16 Diagnostic Register 1-19                    |

| 1.17 Device Space on the MOS Bus                 |

| 1.18 Timer Chip Logic                            |

| 1.19 Interrupt Register                          |

| 1.20 EEPROM 1–21                                 |

| 1.21 Boot PROM1-22                               |

| 1.22 Serial Communication Controllers 1-22       |

| 1.23 Ethernet Interface                          |

| 1.24 VME Bus Interface                           |

| 1.25 CPU Resets 1-23                             |

| 1.26 System Summary Specifications               |

|                                                  |

| CHAPTER TWO: SYSTEM BUS OVERVIEW                 |

| Overview                                         |

| 2.1 68020 Bus Operations and                     |

| Transfer Mechanisms                              |

| 2.2 Read Bus Operations                          |

| 2.3 Write Bus Operations                         |

| 2.4 Bus Error Operations                         |

| and BER Register                                 |

| 2.5 Read-Modify-Write Bus Cycles                 |

| 2.6 CPU Space Cycles 2-9                         |

٠

| 2.7 68881 Floating Point Processor Cycles 2-9 |  |

|-----------------------------------------------|--|

| 2.8 Interrupt Bus Operations                  |  |

| 2.9 Interrupt Acknowledge and Processing 2-12 |  |

| 2.10 Spurious Interrupt Error Processing 2–14 |  |

| 2.11 Bus Arbitration on the Sun 3 System 2-15 |  |

| 2.12 DVMA Operations                          |  |

| 2.13 DVMA Control Logic                       |  |

| 2.14 The VME Bus Interface                    |  |

| 2.15 Ethernet Interface and                   |  |

| Data Transfer Control                         |  |

| 2.16 Ethernet Transactions                    |  |

| 2.17 On-Board Video Display                   |  |

| Frame Buffer Cycles                           |  |

| 2.18 Sun 3 Technical Overview 2-28            |  |

|                                               |  |

| CHAPTER THREE: SYSTEM CONFIGURATION 3–1       |  |

| Overview                                      |  |

| 3.2 System User Switches                      |  |

| 3.3 Sun 3/160M and 3/160C                     |  |

| System Layout                                 |  |

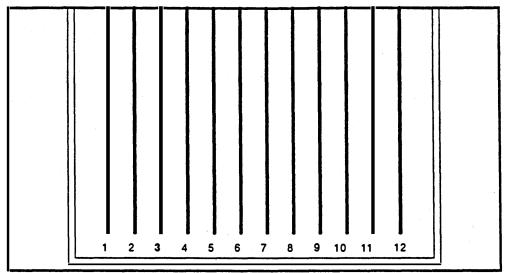

| 3.4 Pedestal Card Cage Layout                 |  |

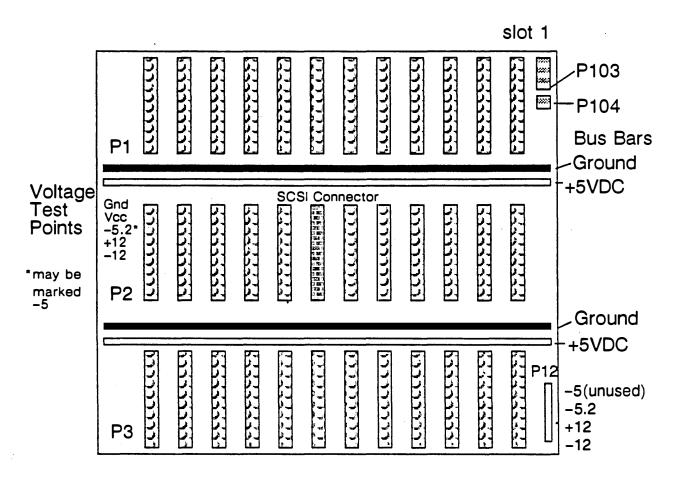

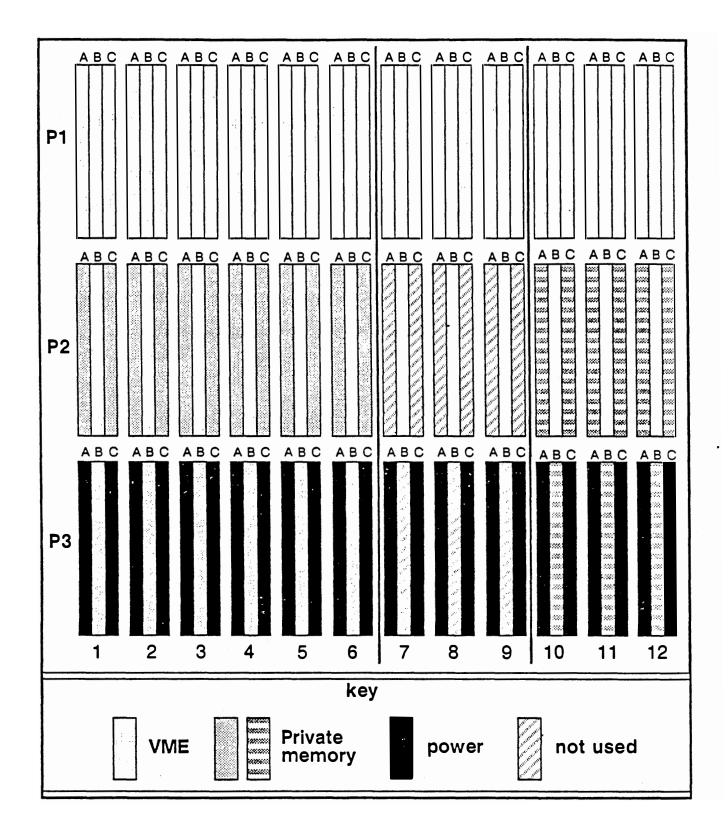

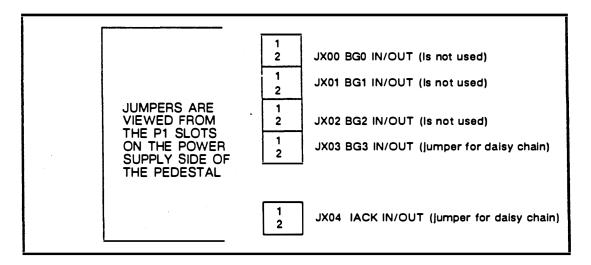

| 3.5 Jumpering the Backplane                   |  |

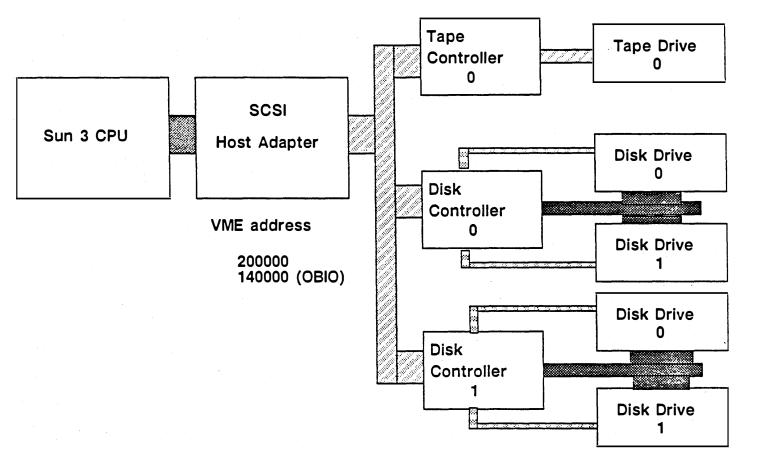

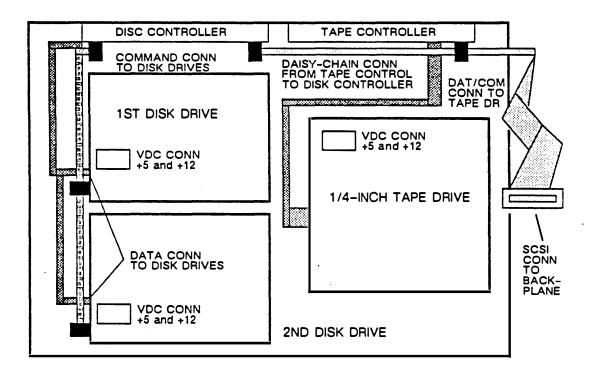

| 3.6 The SCSI Subsystem                        |  |

| 3.8 Power Supply Options and consumption      |  |

| of the Workstations                           |  |

| 3.9 Environmental Specifications              |  |

| 3.10 Sun 3 Memory Configuration               |  |

| 3.11 Sun 3/180FS Rack Mountable               |  |

| File Server                                   |  |

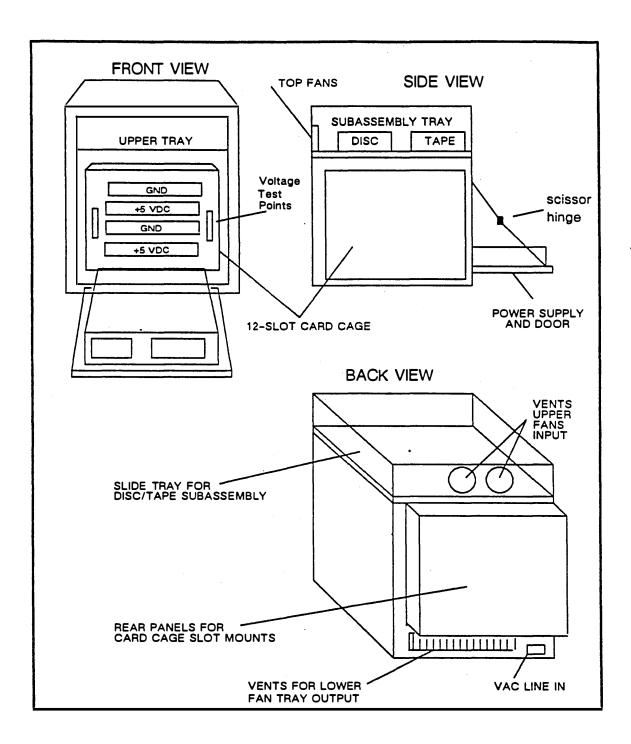

| 3.12 Physical Description                     |  |

| 3.13 The Chassis Module                       |  |

| 3.14 The Fan Tray Module                      |  |

| 3.15 The Power Tray Module                    |  |

| 3.16 System Options for the Sun 3/180FS 3-23  |  |

| 3.17 Sun 3 CPU card configuration 3-24        |  |

| CHAPTER FOUR: DIAGNOSTICS AND                 |  |

| TROUBLESHOOTING                               |  |

| Overview                                      |  |

|                                               |  |

.

-

| 4.1 Prom based self test                        |  |

|-------------------------------------------------|--|

| Diagnostic Structure                            |  |

| 4.2 Resident Boot PROM Diagnostic and           |  |

| User Switch                                     |  |

| 4.3 The Self Test Portion of the                |  |

| Boot PROM                                       |  |

| 4.4 Description of the Self Test                |  |

| Diagnostics                                     |  |

| 4.5 Self Test Failures, Display and Meaning 4-6 |  |

| 4.6 Using the Optional Test Menu                |  |

| 4.7 Using the Monitor Commands                  |  |

| 4.8 Calling Up Monitor Arguments                |  |

| 4.9 Tape based Diagnostics                      |  |

| 4.10 Using DIAG forn an Install Tape 4-27       |  |

| 4.1 1 Sysdiag4-27                               |  |

| 4.12 Troubleshooting Flowcharts4-28             |  |

|                                                 |  |

| CHAPTER FIVE: USING THE EEPROM                  |  |

| Overview                                        |  |

| 5.1 Programming the EEPROM 5-1                  |  |

| 5.2 Changing the EEPROM Values                  |  |

| CHAPTER SIX: DISPLAY CHARACTERISTICS            |  |

| Overview                                        |  |

| 6.1 Technical Features on the Color Display 6-1 |  |

| 6.2 Color Monitor Modules                       |  |

| 6.3 CRT Module                                  |  |

| 6.4 Power Supply Module                         |  |

| 6.5 Deflection Module                           |  |

| 6.6 Video Amplifier Module                      |  |

| 6.7 Digital Dynamic Convergence Module 6–3      |  |

| 6.8 Monitor Interface                           |  |

| 6.9 Degaussing the Monitor                      |  |

| 6.10 The Monochrome Monitor                     |  |

| 6.11 The Power Supply Module                    |  |

| 6.12 The Deflection Module                      |  |

| 6.13 The High Voltage Flyback Module6-8         |  |

| 6.14 The Video Amplifier Module                 |  |

| 6.15 Monochrome Monitor Adjustments             |  |

|                                                 |  |

#### CHAPTER SEVEN: SECTION A

| THE SUN 3 SCSI INTERFACE             |

|--------------------------------------|

| Overview                             |

| 7A.1 SCSI Bus Interface              |

| 7A.2 Interface Control Register      |

| 7A.3 SCSI Bus Controller7A-4         |

| 7A.4 SCSI Data Register              |

| 7A.5 Control Status Register         |

| 7A.6 Parity Logic                    |

| 7A.7 SCSI Request Sensing            |

| 7A.8 SCSI Acknowledge Generation7A-6 |

| 7A.9 DMA Control                     |

| 7A.10 DMA Address Register           |

| 7A.11 DMA Cycle Generator7A-7        |

| 7A.12 VME DMA7A-8                    |

| 7A.13 Request Generation7A-8         |

| 7A.14 Arbitration                    |

| 7A.15 Timing Generation              |

| 7A.16 DMA Overrun7A-9                |

| 7A.17 SCSI Interrupts7A-10           |

| 7A.18 Physical Layout & Setting7A-11 |

.

#### CHAPTER SEVEN: SECTION B

| THE SUN 3 COLOR-GREYSCALE BOARD 7B-1 |

|--------------------------------------|

| Overview                             |

| 7B.1 Power                           |

| 7B.2 Initialization                  |

| 7B.3 Timing                          |

| 7B.4 VME Interface                   |

| 7B.5 VME Interrupt Cycles            |

| 7B.6 Memory Timing 7B-6              |

| 7B.7 Frame Buffer Addressing         |

| 7B.8 Frame Buffer Input Data Paths   |

| 7B.9 Frame Buffer Output Data Paths  |

| 7B.10 TTL Shadow Color Map 7B-10     |

| 7B.11 Horizontal State Machine       |

| 7B.12 Vertical State Machine7B-11    |

| 7B.13 Color Maps and DACS 7B-11      |

| 7B.14 Rasterop Architecture          |

| •         |           |             |       |

|-----------|-----------|-------------|-------|

| 7B.15 The | Greyscale | Application | 7B–15 |

#### CHAPTER SEVEN: SECTION C

| VME/MULTIBUS ADAPTER                             |

|--------------------------------------------------|

| Overview                                         |

| 7C.1 Adapter Configuration Considerations 7C-1   |

| 7C.2 VME Bus to Multibus Addressing              |

| 7C.3 Multibus to VME Bus Addressing              |

| 7C.4 Data Transfers To and From the Adapter 7C-4 |

| 7C.5 Bus Request/Bus Grant Logic                 |

| 7C.6 Interrupt Logic                             |

| 7C.7 VME DMA Cycle                               |

| 7C.8 Clock Logic 7C-7                            |

| 7C.9 SUN 3 VME/MB ADAPTER SETTINGS 7C-7          |

#### CHAPTER SEVEN: SECTION D

•

| GRAPHICS PROCESSOR OPERATION         |         |

|--------------------------------------|---------|

| AND CONFIGURATION                    | . 7D–1  |

| Overview                             | . 7D–1  |

| 7D.1 Graphics Processor Bus Logic    | . 7D–3  |

| 7D.2 VME Interface                   | . 7D–4  |

| 7D.3 VME Transceivers                | . 7D–5  |

| 7D.4 Clock Logic                     | . 7D–7  |

| 7D.5 Reset Logic                     | . 7D–8  |

| 7D.6 VME Slave Control and           |         |

| Address Decode                       | . 7D–8  |

| 7D.7 Slave Synchronizer and          |         |

| Control Latches                      | . 7D–10 |

| 7D.8 Slave Control States            | . 7D–11 |

| 7D.9 Board ID                        | . 7D-12 |

| 7D.10 GP Status/Control Register     | . 7D–12 |

| 7D.11 Microstore VME Address         |         |

| Counter/Data Transceiver             | . 7D–12 |

| 7D.12 Shared Memory Interface and    |         |

| Register Control                     | . 7D–15 |

| 7D.13 Shared Memory Address Pointers | . 7D–16 |

| 7D.14 Shared Memory In/Out           |         |

| Data Registers                       | . 7D–16 |

| 7D.15 Viewing Processor and          |         |

| Support Logic Overview               | . 7D–17 |

|                                      |         |

| 7D.16 VP Instruction Register            | . 7D-18 |

|------------------------------------------|---------|

| 7D.17 VP Bus Source/Destination          |         |

|                                          | . 7D–19 |

| 7D.18 Microsequencer                     | . 7D–19 |

| 7D.19 Viewing Processor                  | . 7D–20 |

| 7D.20 Miscellaneous Controls             | . 7D–21 |

| 7D.21 Floating Point Logic               | . 7D–21 |

| 7D.22 Weitek Floating Point Chips        | . 7D-23 |

| 7D.23 VP PROM and PROM Pointer           |         |

| 7D.24 FIFO Buffer                        | . 7D–25 |

| 7D.25 Painting Processor Logic           | . 7D–27 |

| 7D.26 Instruction Register               | . 7D–28 |

| 7D.27 PP Source and Destination          |         |

|                                          |         |

| 7D.28 PP Microsequencer Logic            | . 7D–30 |

| 7D.29 Scratchpad Memory                  |         |

| 7D.30 VME Master Interface               |         |

| 7D.31 VME Bus Request Logic              |         |

| 7D.32 Data Transfer Controller Logic     |         |

| 7D.33 Timeout Counter Logic              |         |

| 7D.34 Miscellaneous VME Master Logic     |         |

| 7D.35 VME Bus Interrupt Logic            |         |

| 7D.36 Adding A Graphics Processor/Buffer |         |

| 7D.37 GP2 Architecture                   |         |

| 7D.38 GP2 Pipeline                       |         |

| 7D.39 GP2 Shared Memory                  |         |

| 7D.40 GP2 Transform Processor            |         |

| 7D.41 GP2 Rendering Processor            |         |

| 7D.42 GP2 Pixel Processor                |         |

| 7D.43 GP2 Z-Buffer                       |         |

| 7D.44 GP2 Frame Buffer                   |         |

| 7D.45 GP2 Performance                    |         |

| 7D.46 GP2 Configuration Introduction     |         |

| 7D.47 GP2 Kernel Configuration           |         |

| 7D.48 GP2 Device Files                   |         |

| 7D.49 GP2 Creating /dev/cgtwo*           |         |

| 7D.50 GP2 Multiple GP's and /etc/mknod   |         |

| 7D.51 GP2 Using gpconfig                 |         |

| 7D.52 GP2 How to run gpconfig            |         |

| 7D.53 GP2 Microcode Files                | 7D-48   |

| 7D.54 GP2 Graphics Buffer  | 7D-48   |

|----------------------------|---------|

| 7D.55 GP2 Invoking suntool | s 7D-34 |

.

#### CHAPTER SEVEN: SECTION E

| GRAPHICS BUFFER: THEORY            |      |

|------------------------------------|------|

| OF OPERATION                       | 7E-1 |

| Overview                           | 7E-1 |

| 7E.1 Graphics Buffer Memory Array7 | 7E-1 |

| 7E.2 Integer Multiplier Logic      | 7E-2 |

| 7E.3 GB Configuration And Layout   | 7E-3 |

٠

#### CHAPTER SEVEN: SECTION F

| FPA BOARD                                     | 7F-1 |

|-----------------------------------------------|------|

| Overview                                      | 7F-1 |

| 7F.1 Floating Point Operations                | 7F-1 |

| 7F.2 FPA Bus Interface                        | 7F-2 |

| 7F.3 FPA Addressing And Data Path             | 7F-3 |

| 7F.4 Adding The FPA To An Existing System . T | 7F-6 |

#### CHAPTER SEVEN: SECTION G

| ASYNCHRONOUS LINE MULTIPLEXER 2                    | 7G–1 |

|----------------------------------------------------|------|

| Overview                                           | 7G-1 |

| 7G.1 Characteristics                               | 7G-1 |

| 7G.2 Architectural Overview                        | 7G-2 |

| 7G.3 ALM-2 VME Board                               | 7G-4 |

| 7G.4 Device Connector Assembly                     | 7G-4 |

| 7G.5 Installing the ALM-2                          | 7G-7 |

| CHAPTER SEVEN: SECTION H<br>GP2/CG5                | 7H-1 |

| CHAPTER SEVEN: SECTION I<br>TAAC-1                 | 7 -1 |

| CHAPTER SEVEN: SECTION J<br>Sunlink Channel Attach | 7J–1 |

| CHAPTER EIGHT: SUN 3/50                        |

|------------------------------------------------|

| DESKTOP WORKSTATION                            |

| Overview                                       |

| 8.1 3/50 Single-Board Desktop                  |

| System Layout                                  |

| 8.2 Bus Layout On The 3/50 CPU Card 8-3        |

| 8.3 3/50 Resets8-6                             |

| 8.4 Memory Management Unit                     |

| 8.5 The DVMA Channel                           |

| 8.6 On-Board I/O Devices                       |

| 8.7 Input/Output Controller(IOC)               |

| 8.8 Memory Management Unit Control(MMU) 8-11   |

| 8.9 The Main Memory and Support Logic 8-11     |

| 8.10 Video Buffer and Control                  |

| 8.11 Parity Error Logic                        |

| 8.12 The Ethernet Interface                    |

| 8.13 The SCSI Interface and Control Logic 8-14 |

| 8.14 System Specification Summary              |

| 8.15 Configuring The 3/50                      |

| 8.16 Power Supply Specifications               |

| 8.17 The EEPROM 8–19                           |

#### CHAPTER NINE:

.

| 3/110 THREE-SLOT COLOR WORKSTATION . 9-1            |

|-----------------------------------------------------|

| Overview                                            |

| 9.1 Architectural Overview                          |

| 9.2 CPU Space                                       |

| 9.3 Control Space                                   |

| 9.4 Device Space                                    |

| 9.5 Main Memory                                     |

| 9.6 Video Memory                                    |

| •                                                   |

| 9.7 Video Color Map And Output Logic 9-6            |

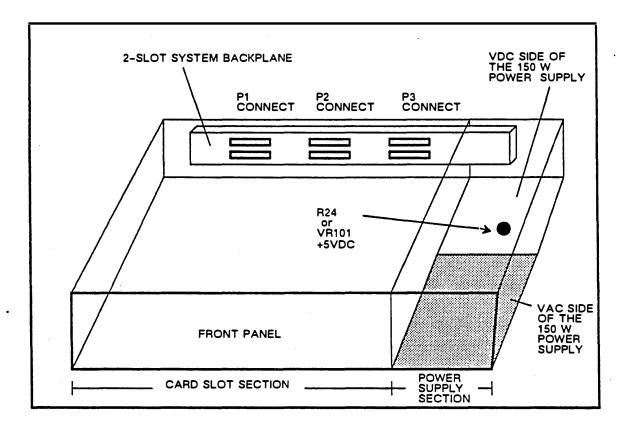

| 9.8 Three Slot Card Cage Configuration 9-10         |

| 9.9 The Sun 3/110 Backplane                         |

| 9.10 The Power Supply Module                        |

| 9.11 Diagnostics and Troubleshooting Section . 9-12 |

| 9.12 Power On Self Test                             |

| 9.13 Extended Diagnostics                           |

| 9.14 The 15-Inch Color Monitor                      |

-

•

CHAPTER TEN:

•

|       | SUN 3/200 SERIES PROCESSOR AND MEMORY             |

|-------|---------------------------------------------------|

|       |                                                   |

|       | Overview                                          |

|       | 10.1 The 3/200 Processor Board 10-1               |

|       | 10.2 Sun 3 Cache 10-4                             |

|       | 10.3 The 3/200 Bus Specification                  |

|       | 10.4 Sun 3 ECC Memory 10-7                        |

|       | 10.5 Memory Configuration 10-9                    |

|       | 10.6 Memory Board Indicators 10-10                |

|       | 10.7 Video Frame Buffer And Support Logic . 10-11 |

|       | 10.8 3/200 CPU And Memory Board Layout 10-13      |

|       | 10.9 Power On Self Test 10-18                     |

|       | 10.10 3/200 Prom Based POR Execution 10-19        |

|       | 10.11 Extended Menu Tests 10-25                   |

| CHAPT |                                                   |

|       | 3/60 Desktop Color Workstation                    |

|       | Overview                                          |

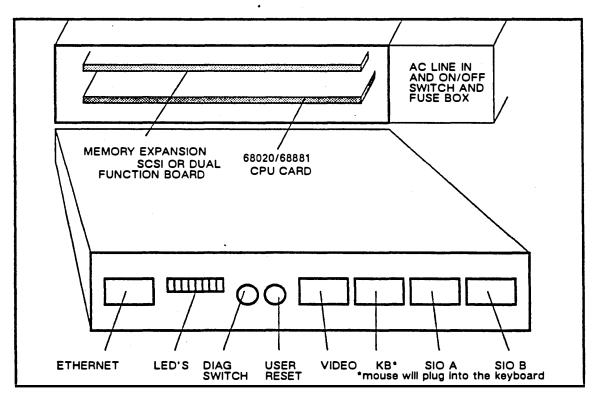

|       | 11.1 Architectural Overview                       |

|       | 11.2 CPU Space 11-2                               |

|       | 11.3 Control Space 11-2                           |

|       | 11.4 Device Space 11-2                            |

|       | 11.5 Main Memory 11-3                             |

|       | 11.6 DVMA 11–6                                    |

|       | 11.7 Ethernet                                     |

|       | 11.8 SCSI 11–7                                    |

|       | 11.9 Video                                        |

|       | 11.10 Backplane 11-9                              |

|       | CPU Jumpers 11-10                                 |

|       | CPU card layout 11-11                             |

|       | 11.11 SIMM Configuration 11–11                    |

|       | 11.12 Color Board Configuration                   |

|       | 11.13 Power Module 11–13                          |

|       | 11.14 Power Supply Adjustments 11–13              |

|       | 11.15 Diagnostics and Troubleshooting 11–13       |

|       | 11.16 Power on Self Tests 11–13                   |

|       | 11.17 Extended Diagnostics 11–17                  |

11.19 Degaussing the Color Monitor ......11-27

APPENDICIES

.

Appendix A: GENERIC Kernel

.

.

.

- Appendix B: Adding Options to Sun 3 Systems

- Appendix C: Troubleshooting Tables

Appendix D: 3E Products

Appenxid E: Lab Projects

#### CHAPTER ONE

#### SUN 3 ARCHITECTURAL OVERVIEW

#### OVERVIEW

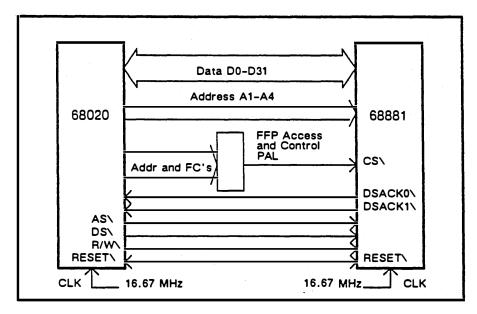

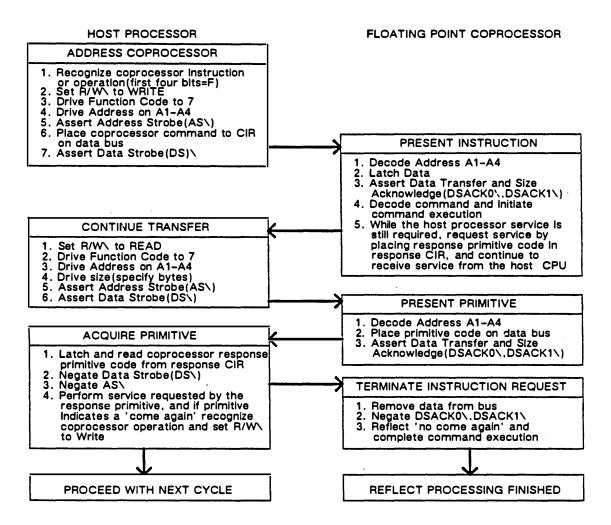

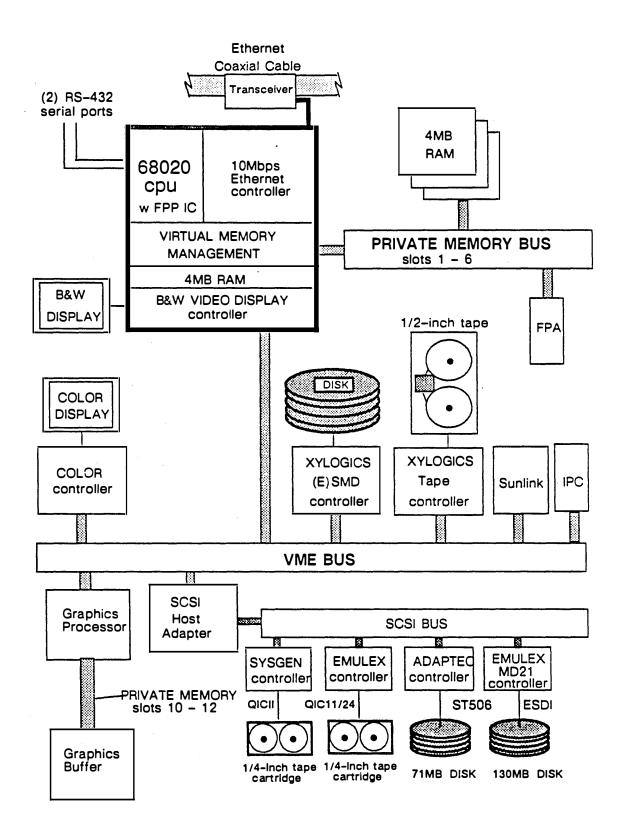

This training manual provides a detailed study of Sun 3 architecture as It is implemented on the Sun 3 workstation product line. Sun 3 architecture implements the processing power and capabilities of the 68020 32-bit microprocessor, in a VME bus environment, and adds enhanced floating-point operations extended with the 68881 floating-point coprocessor.

The following sub-sections are an overview of the architecture in functional blocks and will seldom go to component level detail. Occasional references are made to specific component characteristics necessary to describe a Sun 3 operation.

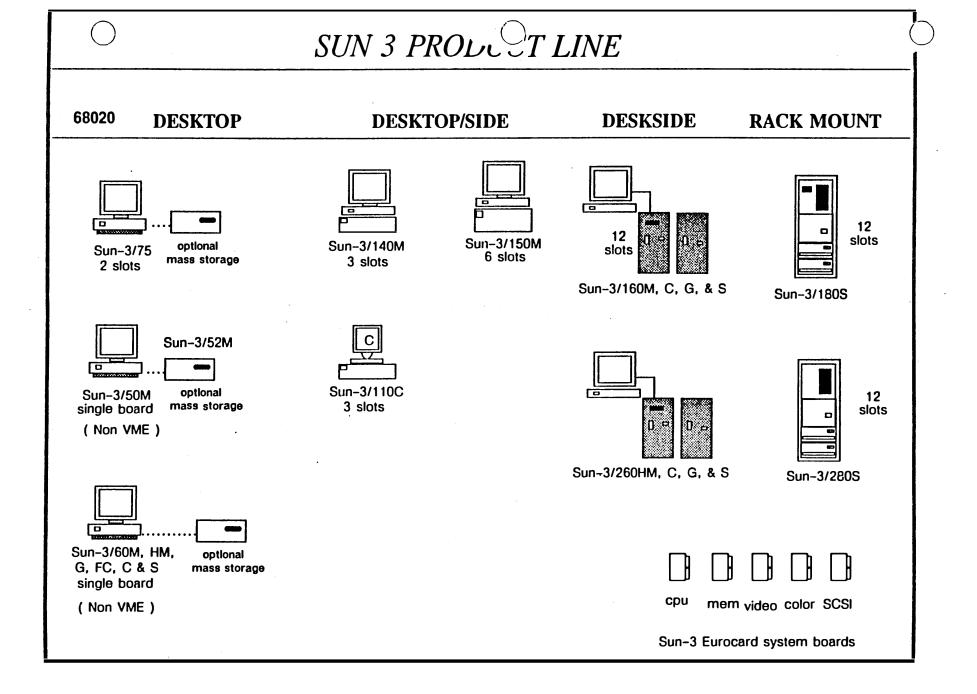

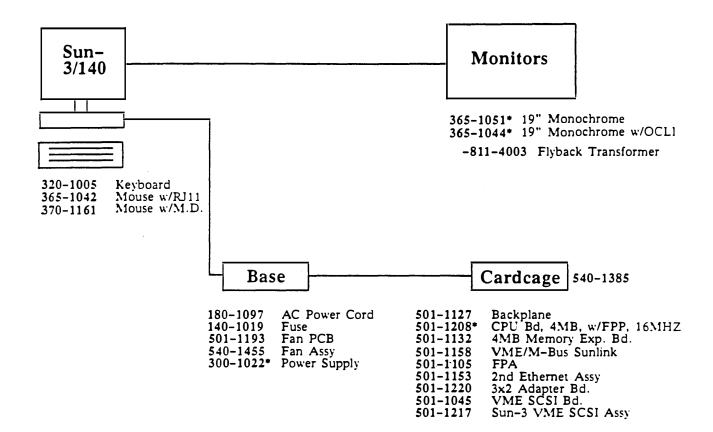

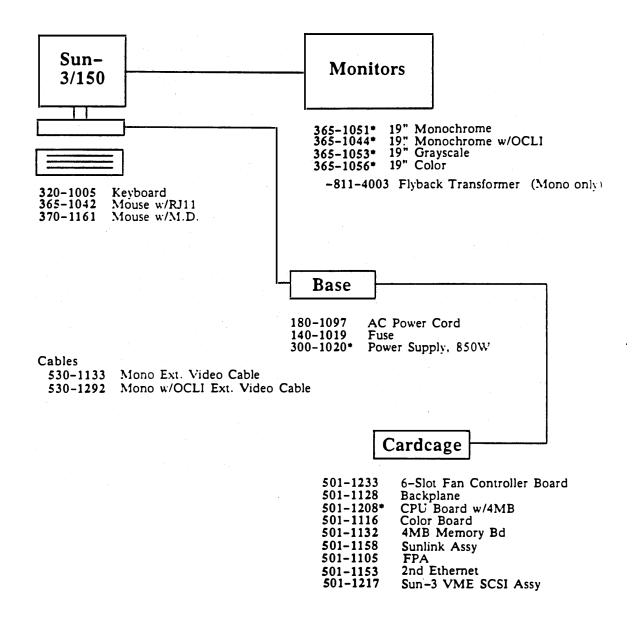

What this manual will contain is a detailed view and introduction to the 68020 microprocessor, how it is used in Sun 3 architecture, and how Sun 3 products comply with the VME bus specification. This manual only covers the current release of SUN 3 products. At the release time of this manual, the Sun 3 product line included: the 3/75M, a general purpose desktop workstation, the 3/140, a 3 slot version with the Sun 3 CPU, and the 3/150, a six slot system using the same technology as the 3/140; the 3/160M/G/HM/C (monochrome, greyscale, hi-res monochrome, and color), a 12-slot pedestal workstation; the 3/180FS, a 12-slot file server; the 3/50, a low cost single board system; the 3/110C, a 3-slot, low cost color workstation: the 3/200 series, a 25 MHz high end workstation with high resolution video display; and the 3/60, a single board desktop color workstation. The following is a summary of the features found on each system.

|                                                                                                                                                                            |                                                                                                                                                                         |                                                                      | 1                                                                                                                       |                                                             |                                                                                                                        |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--|

| SUN 3/75, 140 and 150                                                                                                                                                      | SUN 3/160M or 3/180FS                                                                                                                                                   |                                                                      |                                                                                                                         | SUN 3/160C or G                                             |                                                                                                                        |  |

| 68020 at 16.67 MHz                                                                                                                                                         | 68020 at 16.67 MHz                                                                                                                                                      |                                                                      | 68020 at 16.67 MHz                                                                                                      |                                                             |                                                                                                                        |  |

| 68881 at 16.67 MHz                                                                                                                                                         | 68881 at 1                                                                                                                                                              | 6.67 M                                                               | Ηz                                                                                                                      | 68881                                                       | at 16.67 MHz                                                                                                           |  |

| 4 MB memory standard<br>Demand-paged virtual<br>memory at 256 MB addr<br>space/process, total<br>memory expansion option<br>can be up to 16 MB                             | 4 MB memory standard<br>Demand-paged virtual<br>memory at 256 MB add<br>space/process, total<br>memory expansion opt<br>can be up to 16 MB                              |                                                                      | rtual<br>B addr<br>tal<br>n option                                                                                      | Dema<br>memo<br>space<br>memo                               | memory standard<br>nd-paged virtual<br>ory at 256 MB addr<br>d/process, total<br>ory expansion option<br>e up to 16 MB |  |

| 2, 3 or 6 slot cardcage                                                                                                                                                    | 12-slot ca                                                                                                                                                              | rd cage                                                              | {                                                                                                                       | 12-slo                                                      | ot card cage                                                                                                           |  |

| 19-inch landscape mono-<br>chrome monitor at<br>1152 x 900 x 1 resolution                                                                                                  | ndscape mono-<br>onitor at 19-inch landscape mo<br>chrome monitor at                                                                                                    |                                                                      | t l                                                                                                                     | monitor at<br>1152 x 900 x 8 resolution                     |                                                                                                                        |  |

| Refresh rate at 66 Hz,<br>non-interlaced                                                                                                                                   | Refresh ra<br>non-interla                                                                                                                                               |                                                                      | Hz,                                                                                                                     |                                                             | 56 displayed colors, palette is over 16 M                                                                              |  |

| 32-bit VME bus                                                                                                                                                             | 32-bit VN                                                                                                                                                               | 1E bus                                                               |                                                                                                                         | Graph                                                       | ics processor and                                                                                                      |  |

| Add-on sub-system<br>storage(1/4-inch tape,<br>and/or 71-327 MB drive,<br>formatted.                                                                                       | option for                                                                                                                                                              | mmunication SunLink<br>ion for SNA and BSC<br>vironments and routing |                                                                                                                         | graphics buffer for<br>enhanced high-resolution<br>graphics |                                                                                                                        |  |

| SUN 3/50                                                                                                                                                                   | 8 or 16 ch<br>line multip                                                                                                                                               | annel a                                                              | synch                                                                                                                   | Refresh rate at 66 Hz,<br>non-interlaced                    |                                                                                                                        |  |

| 15 MHZ 68020,optional<br>68881. Single slot system.                                                                                                                        |                                                                                                                                                                         | EEE 796 adapter.<br>E adapter optn                                   |                                                                                                                         |                                                             |                                                                                                                        |  |

| The 3/50 has on-board<br>SCSI control logic, and<br>features VLSI CMOS<br>gate arrays. User can use<br>on board transcievers for<br>coax ethernet or standard<br>ethernet. | Note that the 3/180 is<br>a 19-inch rack mountable<br>system, and can include<br>a 1/2-inch tape sub-<br>system, and a large capa-<br>city mass storage sub-<br>system. |                                                                      | 8 or 16 channel asynch<br>line multiplexer(ALM)<br>VME/MB IEEE 796 adapter<br>or 3/2 VME adapter optn<br>32-bit VME bus |                                                             |                                                                                                                        |  |

| SUN 3/110C                                                                                                                                                                 |                                                                                                                                                                         |                                                                      |                                                                                                                         | 101 2/20                                                    | 0 SERIES                                                                                                               |  |

| 3011 371100                                                                                                                                                                |                                                                                                                                                                         |                                                                      | 50                                                                                                                      | JN 3720                                                     |                                                                                                                        |  |

| 68020 at 16.67 MHz 3-s                                                                                                                                                     | lot system                                                                                                                                                              | 68020                                                                | ) at 25.00                                                                                                              | ) MHz                                                       | 12-slot system                                                                                                         |  |

| 68881 at 16.67 MHz sup                                                                                                                                                     | port                                                                                                                                                                    | 68881 at 20.00                                                       |                                                                                                                         | ) MHz                                                       | 64-bit data bus                                                                                                        |  |

| 4 MB memory standard(up                                                                                                                                                    | to 12 MB)                                                                                                                                                               | 8 MB                                                                 | ECC me                                                                                                                  | mory st                                                     | andard (up to 32 MB)                                                                                                   |  |

| 128 KB frame buffer, and 1 MB FB 256 KB video<br>for on-board color support 1600 by 1280                                                                                   |                                                                                                                                                                         | (B video I<br>by 1280                                                | FB<br>res.                                                                                                              | 64 KB write back<br>data cache                              |                                                                                                                        |  |

| SUN 3/60                                                                                                                                                                   |                                                                                                                                                                         |                                                                      |                                                                                                                         |                                                             |                                                                                                                        |  |

| 20 MHZ 68020,68881. Single slot system 4MB Memory Std. Up to 24 MB Opt.                                                                                                    |                                                                                                                                                                         |                                                                      |                                                                                                                         |                                                             |                                                                                                                        |  |

| On board Color, Mono or                                                                                                                                                    | HiRes                                                                                                                                                                   |                                                                      | Onboar                                                                                                                  | d SCSI                                                      | Controller                                                                                                             |  |

| User can use onboard transceiver P4 "Piggyback" Bus for all video for coax ethernet                                                                                        |                                                                                                                                                                         |                                                                      |                                                                                                                         |                                                             |                                                                                                                        |  |

Figure 1-0: Sun 3 Workstation Features

#### 1.1 68020 MICROPROCESSOR OVERVIEW

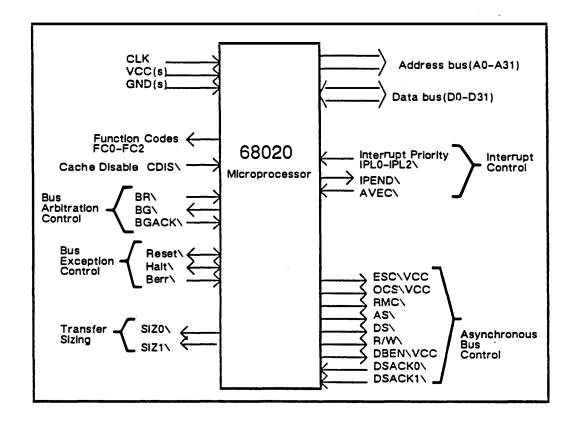

The 68020 microprocessor used in Sun 3 architecture is a 32-bit VLSI device, implemented with an asynchronous bus structure, including 32-bit registers and data paths, 32-bit address registers, and enhanced instruction sets and addressing modes. The 68020 is object code compatible with the 68010 virtual memory microprocessor used in earlier Sun 2 architecture machines.

The 68020 32-bit address and data buses are non-multiplexed bus structures which supports a dynamic bus sizing device that allow the microprocessor to do data transactions with a number of operand size bus devices, including 32-bit, 16-bit and 8-bit data transfer operations.

The 68020 microprocessor on the Sun 3 CPU card runs at 15, 16.67, 20 or 25 Mhz (Model dependent) works with Sun's external virtual memory management unit (MMU) and can interface with other coprocessors such as the 68881 floating point processor.

The 68020 supports the control signal groups (plus some additional control signals) found on earlier Sun 2 68010-based products. Figure 1-1 contains a description of the signal groups.

FIGURE 1-1: 68020 SIGNAL DESCRIPTION

#### 1.3 68020 OPERATIONS

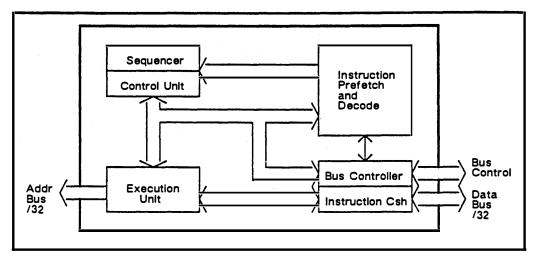

During the execution of a 68020 cycle, the bus controller (illustrated in block form in Figure 1–2) loads instructions from the data bus onto the instruction decode block and the on-chip instruction cache. Note that cache can be controlled by software. The sequencer and control unit block provides for overall chip control, helps in management of the internal buses, as well as the internal registers. This block also provides control for the functions of the execution unit.

The 68020 has 16 32-bit general purpose registers, a 32-bit program counter, a 16-bit status register, a 32-bit vector-base register, two 3-bit function control registers (source and destination), and two 32-bit cache (address and control) registers.

The vector base register is used to determine the location of the exception vector table in memory (where the routine for that particular exception or interrupt handler begins). The status register contains the interrupt priority mask

(3-bit), the condition codes (for branching decisions), trace enable bits, a supervisor/user bit and a Master/Interrupt bit.

FIGURE 1-2: 68020 INTERNAL BLOCK DIAGRAM

#### 1.4 VIRTUAL MEMORY IMPLEMENTATION

The extended addressing range of the 68020 microprocessor is 4 giga bytes. The actual physical memory found will be smaller. Sun uses a 28 bit virtual address, so the extent of virtual address space is 256 Mbytes per process. The other three bits of the VA range are used to construct a context which allows rapid switching between processes.

Using a technique called virtual memory access, a virtual memory based system support is provided for the limited amount of high-speed physical memory that can be accessed directly by the processor, while maintaining a much larger 'virtual memory' on a secondary storage device (such as a large capacity disk drive). This process is designed to support a 'demand paging' scheme.

As the microprocessor attempts to access a location in the virtual memory map, that is not actually residing in the physical memory (page invalid) its access is temporarily suspended while the actual data is fetched from the secondary storage device and written to physical memory, via the demand paging scheme program pointed to by the invalid page exception. The microprocessor can then restart or continue its access cycle. To restart, the 68020 uses instruction continuation for virtual memory management. In order to implement instruction continuation, the 68020 stores its internal state on the supervisor stack when a cycle has been suspended. The 68020 will load the program counter with the address of the virtual memory location, and thus, will be able to restart (continue) with program execution at the new address.

This holds true for bus errors which cause exception processing as well. When the microprocessor bus error exception handler routine has completed, an instruction (RTE=return from exception) is executed to reload the 68020 with the internal state stored on the supervisor stack. The processor can then rerun the faulted bus cycle, or continue (restart) the suspended instruction cycle via the virtual memory map. On Sun 3 architecture, an external memory management unit is provided to support virtual memory. Information on this circuit is provided later on in this section.

#### **1.5 SPACE ORGANIZATION ON SUN 3 ARCHITECTURE**

Sun 3 architecture is divided into three spaces including the CPU space, the control space, and the device space.

The CPU space is comprised of the 68020, and coprocessors such as the 68881 floating point processor.

The control space is considered the core of Sun 3 architecture and includes the Memory Management Unit (MMU) and extensions of the CPU such as the bus error register, the system enable register, the diagnostic register, and the system ID PROM. These devices will be discussed later on in this chapter. The ID PROM will contain the machine 'type' implemented for each respective architecture level (e.g. Sun 3 architecture).

The device space will define the devices that exist in the architecture and how each will be accessed. The devices space includes the main memory, the video frame buffer, the system bus master interface (VME bus), and the I/O devices.

All levels of Sun 3 space types can be accessed by the CPU via the MMU with the exception of the 68881. The CPU can directly access the floating point processor. The primary purpose of the MMU will be to allow access to the devices in a shared and protected environment. The MMU will also manage address translation (from virtual-to-physical addresses) and the context of the current process

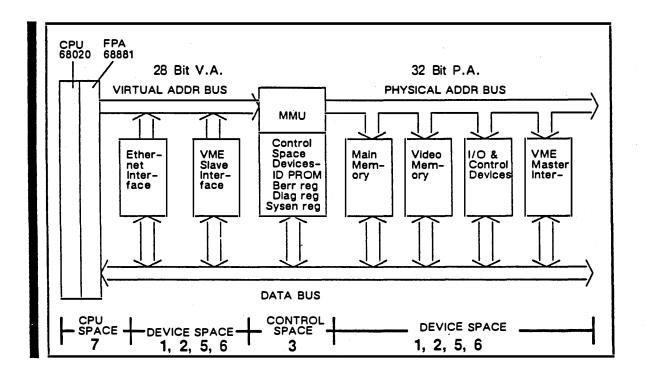

DVMA devices such as Ethernet, SCSI and VME slaves as well as the CPU will arbitrate for (and share) the virtual address bus and will be discussed in the next section. Figure 1–3 illustrates how the CPU, MMU and Devices are connected in Sun 3 architecture.

FIGURE 1-3: ARCHITECTURAL BLOCK OVERVIEW

Sun 3 architecture is divided into three spaces: CPU space, Control space, and Device space. An image of this space division is maintained by the processor (aided by the MMU) to map out the spaces. The Function Code table is used to describe how they are mapped out.

The contents of the Function Code table identify the processor state and the address space of the bus cycle currently being executed. The MMU is used to decode the table (see MMU section) so that the memory system can utilize the 4 GB address range for the space divisions. Figure 1–4 illustrates the Function Code table and space assignment. The MMU section of this overview will describe how they are decoded during the execution of a particular cycle. Note while operating under an operating system, the decoding will also provide useful information on a successful or unsuccessful process cycle.

| FC2 | FC1 | FC0 | CYCLE TYPE               | FC | ADDRESS SPACE           |

|-----|-----|-----|--------------------------|----|-------------------------|

| 0   | 0   | 0   | Undefined, Reserved      | 0  | Reserved                |

| 0   | 0   | 1   | User Data Space          | 1  | Device Space(usr data)  |

| 0   | 1   | 0   | User Program Space       | 2  | Device Space(usr progm) |

| 0   | 1   | 1   | Control devices          | 3  | Control Space           |

| 1   | 0   | 0   | Undefined, Reserved      | 4  | Reserved                |

| 1   | 0   | 1   | Supervisor Data Space    | 5  | Device Space(supr data) |

| 1   | 1   | 0   | Supervisor Program Space | 6  | Device Space(supr prog) |

| 1   | 1   | 1   | CPU Space                | 7  | CPU Space               |

#### FIGURE 1-4: ADDRESS SPACE ASSIGNMENTS

Note that the CPU space uses Function Code level 7. Such space cycles will include the processor, coprocessor, interrupt, breakpoint and ring-protection cycles IE: after an exception. Supervisor space Function codes are generated when the supervisor bit in the status register is on, (FC 6 would be on for an instruction fetch) Control space cycles will be level 3 and include access to the memory management unit (MMU), the bus error register, the system enable register, the diagnostic register and the ID PROM. The device space will include all devices that will be accessed by the CPU with data or program instructions (e.g. main memory, VME bus master interface and I/O devices).

#### 1.7 MEMORY MANAGEMENT UNIT (MMU) OVERVIEW

The purpose of the Memory Management Unit (MMU) is to ensure that devices have access to the memory and to each other in a fully protected, shared and managed, multiprocess environment. The MMU will manage three memory states including:

- 1. The mapped state where a process is resident and mapped into the page map, making the mapped process runable.

- 2. The resident state where the resident process state has a user page and page table in memory.

- 3. The swapped state where a swapped process is completely residing on the secondary storage device (usually the disk).

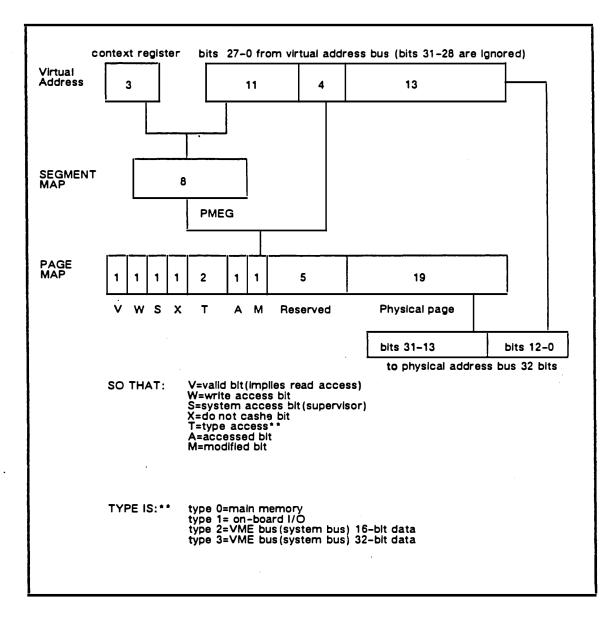

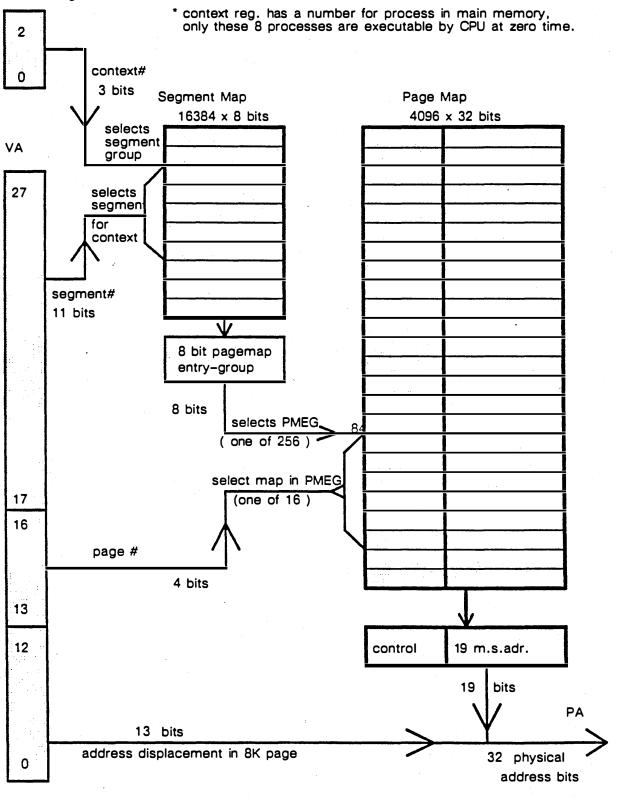

The MMU logic is implemented with a context register, a segment map, and a page map. Virtual addresses from the processor and DVMA devices will be translated into physical addresses by the previously written segment and page maps and previously chosen context.

The MMU uses a page size of 8K bytes and a segment size of 128K bytes. There are 8 separate contexts which can be thought of as processes with an address space of 256M bytes for each context.

The current context is selected ("switched") in the 3-bit context register by a single instruction from the 68020. This has proved to be a highly efficient mechanism to switch from one process to another. This way we can give meaning to a supervisor or user 'context'. In other words, define the context of the address space access by reading the bits in the register. When referring to the context of a cycle, access generate by the the KERNEL will typically operate within a supervisor context, while application processes will operate within a user context.

The Segment map has a total of 16384 entries (refer to Figure 1–5 and 1–6). The segment maps are indexed by the current context (3–bits from the context register) and the 11 most significant bits of the virtual address. The Segment map is divided into 8 contexts of 2048 entries each for a total of 16384 entries.

These segment map entries are 8-bits wide and are used to point to a Page Map Entry Group (PMEG). The PMEG is used as a pointer, producing an intermediate address which will be translated to a physical one via the page map.

The Page Map contains 4096 page entries with each mapping an 8K byte page. The page map entries will be composed of a valid bit, protection field, do not cache bit, type field, access and modification bits, and a page number. Figure 1–5 illustrates this entry field. The page map itself is divided into 256 sections of 16 entries each. Each section, then, will be pointed to by the segment map entry, or PMEG. Refer to Figure 1–5 and 1–6 on the next 2 pages.

#### FIGURE 1-5: MEMORY MANAGEMENT ADDRESS TRANSLATION

VA = virtual address

PA = physical address

| UNIT DESCRIPTION               | SIZE       |

|--------------------------------|------------|

| Page size                      | 8K bytes   |

| Segment size                   | 128K bytes |

| Process size                   | 256M bytes |

| Number of contexts             | 8          |

| Number of segments per context | 2048       |

| Number of pages per segment    | 16         |

| Number of pages                | 256        |

| Number of pages total          | 4096       |

| Number of segments total       | 16384      |

| FIGURE 1–6: MMU SUMMARY ASSIGNMENTS | FIGURE 1 | 1-6: | MMU | SUMMARY | ASSIGNMENTS |

|-------------------------------------|----------|------|-----|---------|-------------|

|-------------------------------------|----------|------|-----|---------|-------------|

#### **1.8 PHYSICAL ADDRESS MAP**

The physical address map is fixed for all implementations of Sun 3 architecture. The number of physical address bits which define a devices address space is dependent on the MMU 'type field' illustrated in Figure 1–5. Figure 1–7 illustrates the physical address assignments used in Sun 3 architecture.

| TYPE | MMU BASE ADDRESS | DEVICE                            |

|------|------------------|-----------------------------------|

| 0    | 0×0000000        | Main Memory                       |

| 1    | 0×0000000        | Keyboard/Mouse                    |

| 1    | 0×00020000       | Serial Ports                      |

|      | 0x00040000       | EEPROM                            |

|      | 0x00060000       | TOD Clock                         |

|      | .0×00080000      | Memory Error Register             |

|      | 0x000A0000       | Interrupt Register                |

|      | 0x000C0000       | Ethernet Interface (if Intel)     |

|      | 0×000E0000       | Color Map                         |

|      | 0×00100000       | EPROM(Boot PROM)                  |

|      | 0x00120000       | Ethernet Interface(If AMD)        |

|      | 0x00140000       | SCSI Interface(3/50 or 3/60 only) |

|      | 0x00160000       | Reserved                          |

|      | 0x00180000       | Reserved                          |

| 1    | 0x001A0000       | Reserved                          |

|      | 0x001C0000       | DEP                               |

|      | 0×001E0000       | Undefined, Reserved               |

| 2    | 0×0000000        | 32-bit address space 🦳            |

|      | 0×FF000000       | 24-bit address space              |

|      | 0×FFFF0000       | 16-bit address space 🤳            |

| 3    | 0×0000000        | 32-bit address space              |

|      | 0×FF000000       | 24-bit address space              |

|      | 0×FFFF0000       | 16-bit address space $\int$       |

#### FIGURE 1-7: PHYSICAL ADDRESS ASSIGNMENTS

#### **1.9 DEVICE AND CONTROL DATA PATHS**

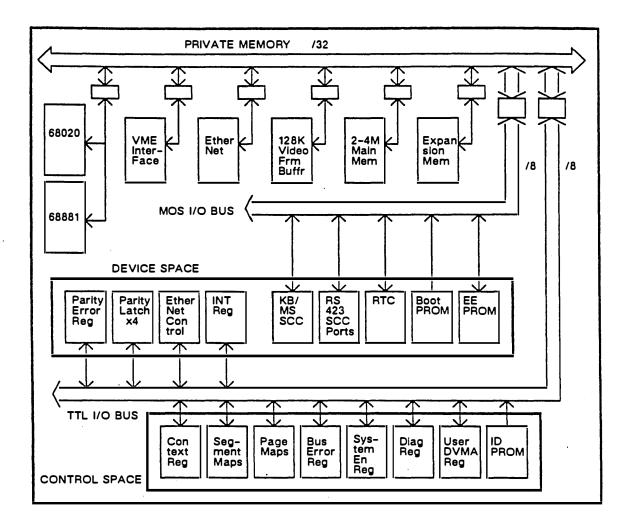

The following sections will cover the device and control logic physically residing on-board the CPU card and interfaced to the 32-bit data bus as well as the byte bus (8-bit) on the CPU card. This will be an overview of the main data path, the MOS data path, and TTL 8-bit data bus, and their respective interface. The bus paths and component groupings in this section will be related in the accompanying block diagram in Figure 1-8 on the following page.

FIGURE 1-8: SUN 3 DATA BUSSING

There are two bus sizes used on the CPU card including the 32-bit and the 8-bit buses. The 32-bit bus provides the high bandwidth data path between the processor, the DVMA devices, the VME bus and the main memory. The 8-bit bus is used to reduce board routing problems during data transaction cycles. This is due primarily to the different driving capabilities between MOS and TTL devices. The MOS devices have weaker bus drivers and are sensitive to undershoot. The TTL devices, on the other hand, have the opposite drive characteristics, and are therefore prone to overshoot.

For devices on the 8-bit bus that will require a larger interface bandwidth, such as the Page Maps, the dynamic bus sizing capability of the 68020 is used so that long word transactions can be accomplished. This holds true for the Parity Latch as well (x4 latch).

#### 1.11 CONTROL DEVICES ON THE TTL BUS

#### 1.12 ID PROM

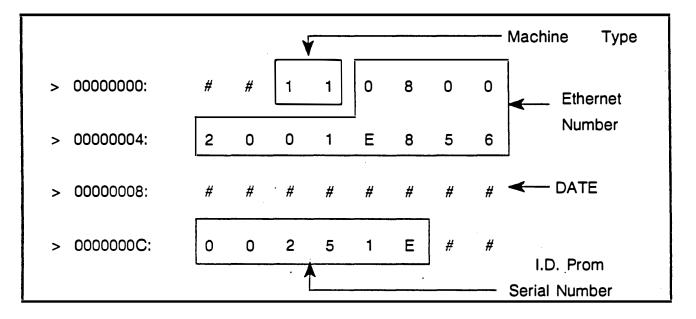

The ID PROM, located on the 8-bit TTL bus, is a read only device which provides the system bus with key information about the machine. The data fields included on this device are the format of the PROM, the machine type-specifying the type of architecture (i.e. Sun 3), the Ethernet address-a unique address assigned to the Sun Workstation, the date the PROM was generated, the serial # of the idprom (not the system serial #), a checksum-specifying the PROMS checksum yield, and a reserved field for future PROM revisions. The ID PROM is read during the BOOT stage, and can be read by initiating a 'K2' reset to the system, or by invoking 'KB'. Figure 1–9 shows the contents of the PROM.

| ENTRY FIELD          | SIZE    |

|----------------------|---------|

| (1) Format           | 1 byte  |

| (2) Machine Type     | 1 byte  |

| (3) Ethernet Address | 6 byte  |

| (4) Date             | 4 byte  |

| (5) Serial Number    | 3 byte  |

| (6) Checksum         | 1 byte  |

| (7) Reserved         | 16 byte |

FIGURE 1-9: ID PROM CONTENTS

Machine Type is user by the Kernel in determining the CPU type on boot.

Ethernet number is used when diskless clients request a server and for low level file transfer.

Unix hostid = Machine Type followed by Serial Number (of I.D. Prom)

Bad or wrong ID PROMs can cause watchdog resets, invalid frame buffers, SCSI boot timeouts, client boot problems and spurious interrupts.

Hostid is used by some companies to protect their products against unauthorized duplication and distribution. Hostid is a SunOs command.

#### EXAMPLE:

#hostid <cr>

1100251E (11=carrera, 00251E=SN# of ID PROM)

## Dumping the I.D. Prom

Address 0x0000000

>s3

>1 0 (lowercase "L", "zero", and <cr> 4 times)

| Code | Name     | Family                           |

|------|----------|----------------------------------|

| 11   | Carrerra | 3/75, 3/140, 3/150, 3/160, 3/180 |

| 12   | Model 25 | 3/50                             |

| 13   | Sirius   | 3/260, 3/280                     |

| 14   | Prism    | 3/110                            |

| 17   |          | 3/60                             |

| 21   | Sunrise  | 4/260, 4/280                     |

| 22   | Cobra    | 4/110                            |

| 02   |          | Sun2·VME                         |

| 01   |          | Sun2 Multibus                    |

#### 1.13 SYSTEM ENABLE REGISTER

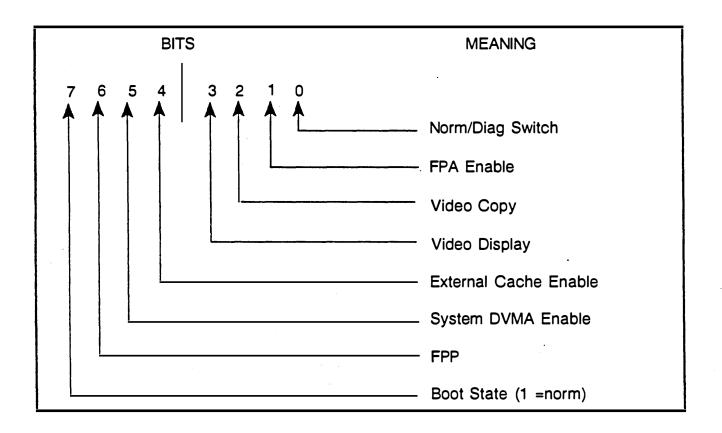

The System Enable register enables the system facilities and allows the BOOT state. The register can be read or written to under software control. During a Power-On-Reset (POR) or Watchdog reset (see reset section), the system enable register is cleared. That is, when it is cleared all 8-bits are set to '0'.

The system enable register sets up the bits that will monitor the state of reading back the diagnostic switch(see switch section), enabling the floating point coprocessor (68881) or FPA, enable the copy mode to video memory and the video display, and will also enable a system DVMA (when present). During a BOOT state, the system enable register is read to the state of the forced BOOT FETCH (i.e a normal state vs a boot state).

#### System Enable Register:

8 bit r/w data register

Address 0x4000000

>s3

>0 4000000

Data displayed is in the form of a two digit hex byte. To interpret the data, you must break each digit down into it's binary bits and identify which bits are set (1) and which are reset (0)

EXAMPLE: Register contains A9 = 10101001 binary Bits 7, 5, 3, and 0 set. This is a normal indication for a 3/160 with it's Norm/Diag Switch in Diag.

# 1.14 USER DVMA ENABLE REGISTER

On cycles which allow user DVMA this register controls which contexts will have DVMA access. Each context will have a separate enable bit provided. During a POR or Watchdog reset the User DVMA enable register bits are set to '0'. While in a reset state, all user DVMA will be disabled.

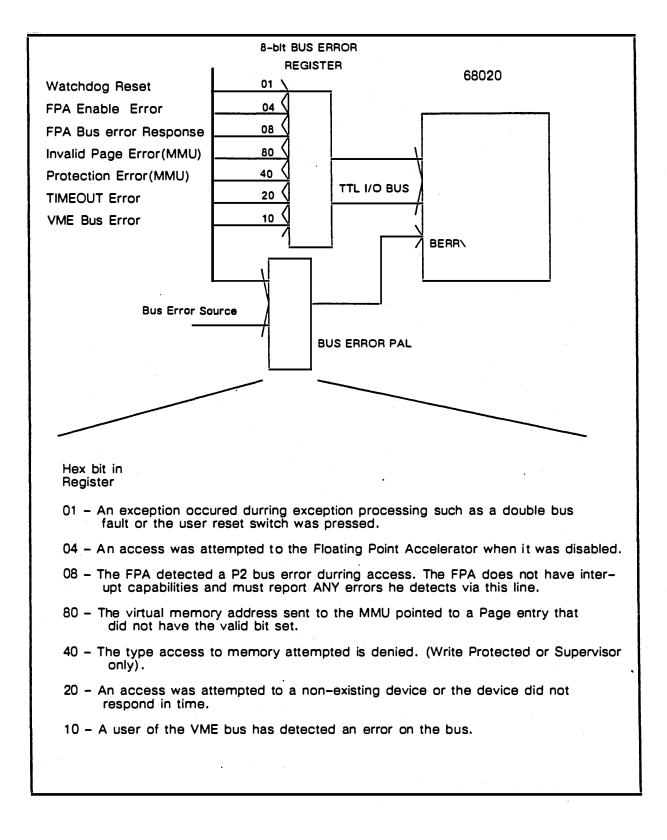

### 1.15 BUS ERROR REGISTER

The Bus Error register is used to latch a bus error which occurs synchronously to a CPU cycle. By latching the error as it occurs, the software can be used to identify the source of the bus error. The synchronous errors can be divided into two groups, those which occur and are identified by the register (when read), and those identified by the CPU itself- by the type of cycle it occurred on.

Examples of bus errors which occur during the cycle, and that are identified by the CPU include spurious interrupts (an error occurring during an Interrupt Acknowledge cycle) or an line instruction interrupt to the floating point processor. Both errors are identified solely by the type of cycle in which they occurred.

The Bus Error register will latch the cause of the pending bus error for the most recent case. If there are stacked bus errors, the data bit relating to the earlier error is lost. The Bus Error register is a read-only device which will monitor floating point enable errors or FPA bus error response, VME bus errors (a CPU cycle to the VME bus was acknowledged with a bus error), timeout errors (resulting from accessing non-existing or non-responding devices on the bus), protection errors(indicating that the page protection bits did not allow the kind of operation attempted during a CPU bus cycle to a valid page) and invalid page errors (indicating that a valid bit in the page map was not set).

# 1.16 DIAGNOSTIC REGISTER

The diagnostic register is used to drive the 8-bit LED display for monitoring error messages. During a cycle error, the insuing error will correspond to the LED display pattern. The diagnostic register will drive the LEDs to all ON during a power-on-reset condition and is a range of addresses beginning at 70,000,000. Refer to the diagnostic section of the manual for a description of the LED table.

# **Diagnostic Status Register**

8 bit write only data register

Address 0x7000000

>s3

>o 7000000 5a (flashes 10100101) >o 7000000 00 (flashes 1111111) >f 7000000 7fffffff 00 (flashes 1111111 for extended period)

\*NOTE \* Register does not latch

# 1.17 DEVICE SPACE ON THE MOS BUS

# 1.18 TIMER CHIP LOGIC

The timer device on the CPU card is an Intersil 7170 time-of-day clock with a battery back-up circuit. The timer crystal oscillates at 32.768KHz. The clock interrupt output causes an interrupt request at level 7 and level 5, via the interrupt register, when the respective levels are enabled.

# **1.19 INTERRUPT REGISTER**

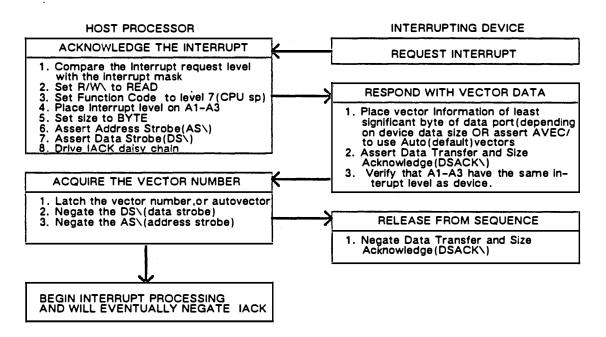

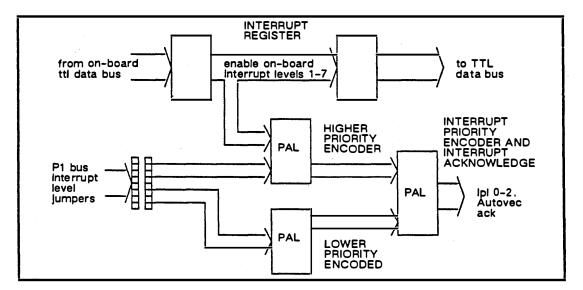

The interrupt register provides for the generation of software interrupts (from interval OS dependent cycles), controls the device hardware interrupts, and the clock interrupts on the CPU board. The register will read in interrupt enable levels for on-board devices.

On-board interrupts will be autovectored on all levels except for level 6. For level 6 (SCC's) the 8530 SCC devices will provide the vector. VME vectored interrupts will be vectored at a lower priority than 0n-board interrupts, and are set by jumpers on the CPU board.

÷.

The chart on the following page lists the interrupts by level and divides them into on board and off board groups for easy reference. Note that a level can have numerous devices, all of which may attempt to interrupt at the same time.

The processor uses the level and the AVEC signal to control interrupting devices and respond to the most urgent request.

# **CPU Interrupt Levels**

| Off Board          | Level | Level On Board      |  |

|--------------------|-------|---------------------|--|

|                    | 7     | NMI & RTC           |  |

|                    | 6     | SCC                 |  |

|                    | 5     | RTC (Unix)          |  |

| ALM                | 4     | Video Vertical Int. |  |

| B/W Graphics       | 4     |                     |  |

| Color Graphics     | 4     |                     |  |

| Graphics Processor | 4     |                     |  |

| 1/2 inch tape      | 3     | Ethernet            |  |

| Second Ethernet    | 3     | Sys enable (4)      |  |

| Xylogics Disk      | 2     |                     |  |

| SCSI               | 2     | Sys enable (2)      |  |

| Versatek           | 2     |                     |  |

|                    | 1     | Sys enable (1)      |  |

### FIGURE 1-10: Off board and On Board Interrupt Levels

By removing the jumpers on the CPU board you can isolate off board interrupt problems.

# 1.20 EEPROM

A EEPROM, implemented with a 2816 device, provides the CPU with 2K bytes of electrically erasable storage parameters. These parameters are primarily set up to provide information about the system, the display (which frame buffer will be defaulted to) and SIO ports (console information), and buffer information describing how the self-test will be accomplished (exclude memory test default). Chapter Five will detail the use and set-up of the EEPROM.

# 1.21 BOOT PROM

The Boot PROM is a 27512 EPROM providing around 64K bytes of bootable code to initialize the system. This read-only device resides on the MOS I/O bus, and is addressed directly with virtual addresses from the processor. The BOOT PROM is accessed during the FORCED BOOT state. While in this state, all supervisor program fetches are forced to fetch from this device, independent of the setting of the MMU. A NORM/DIAG switch on the boards rear edge panel is used to select the normal boot code, or diagnostic code, from the BOOT PROM device while at the MONITOR level.

# **1.22 SERIAL COMMUNICATION CONTROLLERS**

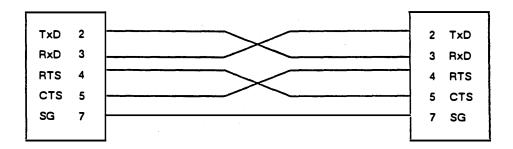

The CPU card provides two Serial Communication Controllers (SCC) for SIO port and keyboard/mouse control (1200 baud). These controllers behave like UARTS, but are programmable. The SCC's are implemented with Zilog 8530's, featuring two high speed, fully symmetrical and programmable serial channels. Both SCC's on the CPU card have built-in baud rate generators.

The SCC controlling the SIO ports uses its channel A for the UART A port, and channel B for UART B port. Both ports are set up for EIA RS 423 specifications, and operate from an independent CPU clock rate at 4.9152MHz. The SCC controlling the keyboard/mouse uses its channel A for the keyboard and channel B for the mouse. The RS 423 devices are signal compatible with RS 232 C, CCITV.24 but limit voltage to +/- 12VDC (refer to EIA specification).

# **1.23 ETHERNET INTERFACE**

The Ethernet interface and control is implemented with an Intel 82586 Ethernet Data Link Controller. Ethernet accesses the top 16 M bytes of the current virtual address space, with the supervisor data function code. The Ethernet interface uses the TYPE 0 space (memory) only, as a DVMA master.

Bus errors can occur during an Ethernet transfer as a result of a protection error or a memory error (parity) during a read operation. If an Ethernet bus cycle concludes with a bus error, the error bit in the Ethernet control register is set and further activity is stopped. Ethernet will reset during an aborted DVMA cycle when a bus error is pending. Like Sun 2 architecture, the 82586 is physically byte swapped on-board the CPU card. This ensures that the Ethernet data is stored in memory in 68020 byte-order.

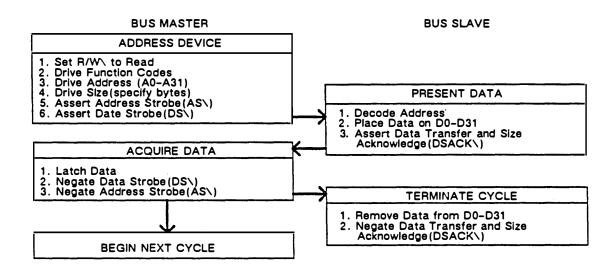

# 1.24 VME BUS INTERFACE

The VME bus interface is dual-ported. The VME bus master interface provides access from the CPU to the VME bus, and the VME slave interface provides access from the VME bus to the CPU.

A VME master is a device which can initiate a transaction over the VME bus. Such as the CPU or the SMD disk controller when they want to store data directly into memory. A VME slave simply responds to such transactions. The CPU board will act as the arbitor and default master.

To meet the VME specification, Sun 3 architecture supports a 32-bit master or slave address bus, (This is the Physical address bus out of the MMU) a 32-bit master or slave data bus, has a minimum timeout period of 739 usec (excluding bus acquisition), supports single level arbitration and a 'release-on-request (ROR)' option, as well as providing interrupt handling.

The VME master interface uses two page map type codes including one for 16-bit data (TYPE 2), and the other for 32-bit data (TYPE 3).

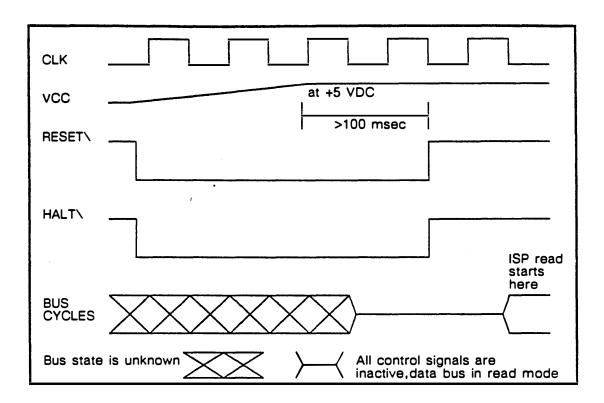

# 1.13 CPU RESETS

There are 5 possible reset sources for Sun 3 architecture. These include POR (active for >100 msec after the power reaches a 4.5 VDC level), VME bus reset (jumperable, when the CPU board is not the arbitor), Watchdog reset (when the CPU halts due to double bus faults), a user reset (initiated via the external reset switch), and a CPU reset (resulting from the CPU executing a RESET instruction).

The power-on-reset (POR) is illustrated below to indicate to the reader what conditions must be met internally to the 68020, before it is stable enough to execute its first instruction fetch

FIGURE 1-11: POWER-ON-RESET(POR) ACTIVITY

When the processor is reset by the external reset circuit (POR or user reset switch) the reset is recognized as a system reset. The processor will attempt to complete the current bus cycle, and will then reset the vector table entry (two words) and load it into the Interrupt Stack Pointer (ISP). This will set the status register to a level 7 (NMI) interrupt mask.

# **1.27 SYSTEM SUMMARY SPECIFICATIONS**

The following table, will give the user a quick reference guide to the system summary specification. Current versions of the Sun 3 product covered include node' the Sun 3/75M 'diskless workstation. the Sun 3/160M monochromatic-based pedestal, and the Sun 3/160C color workstation, the 3/180 file server, and the low cost 3/50- single board system, the Sun 3/110 low cost color workstation, the Sun 3/140 -3 slot version with the Sun 3 CPU, and the Sun 3/200 high end 25 MHz workstation with high resolution display video. See next page.

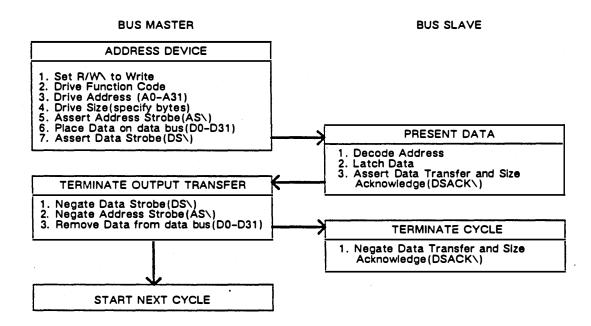

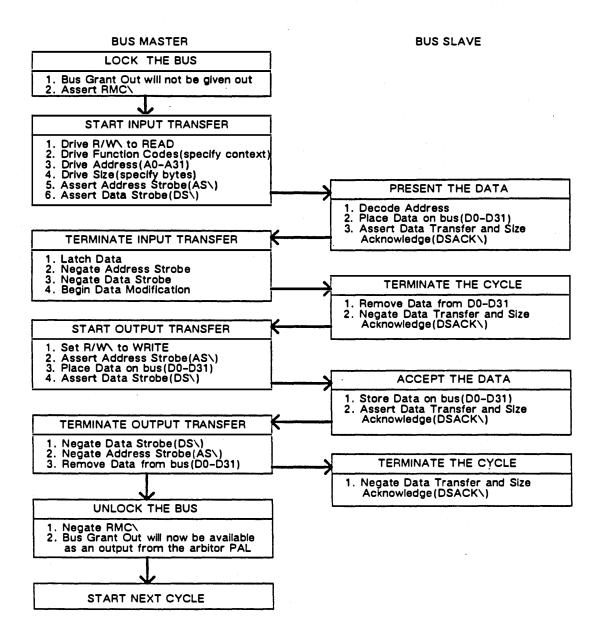

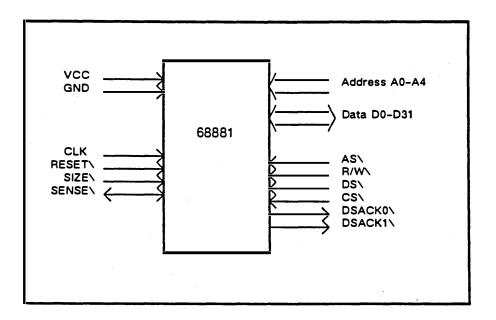

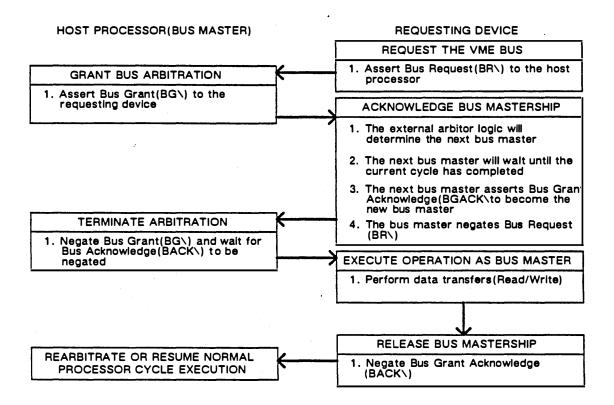

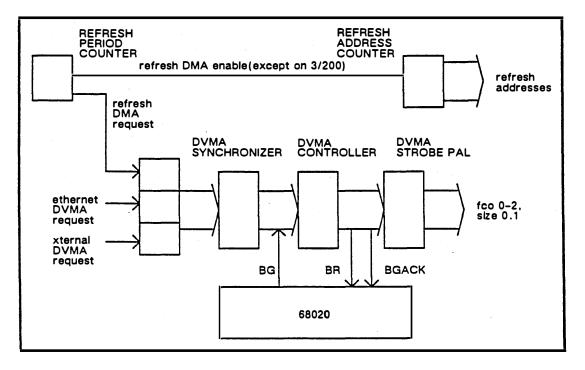

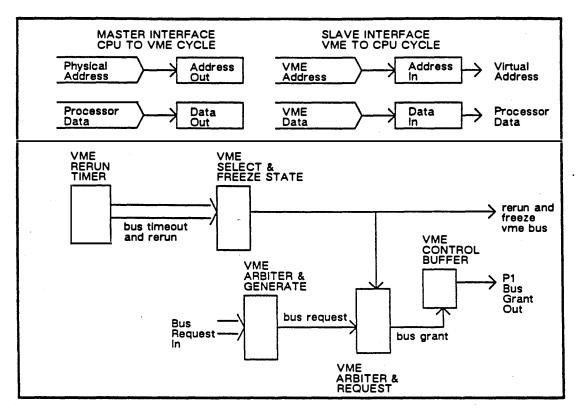

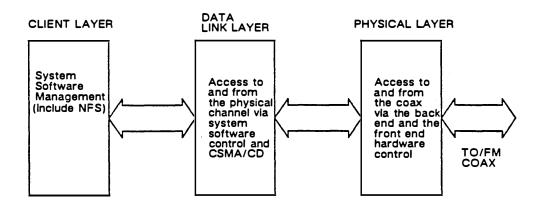

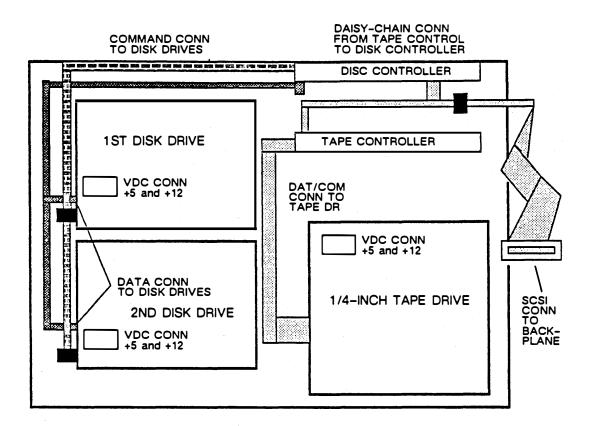

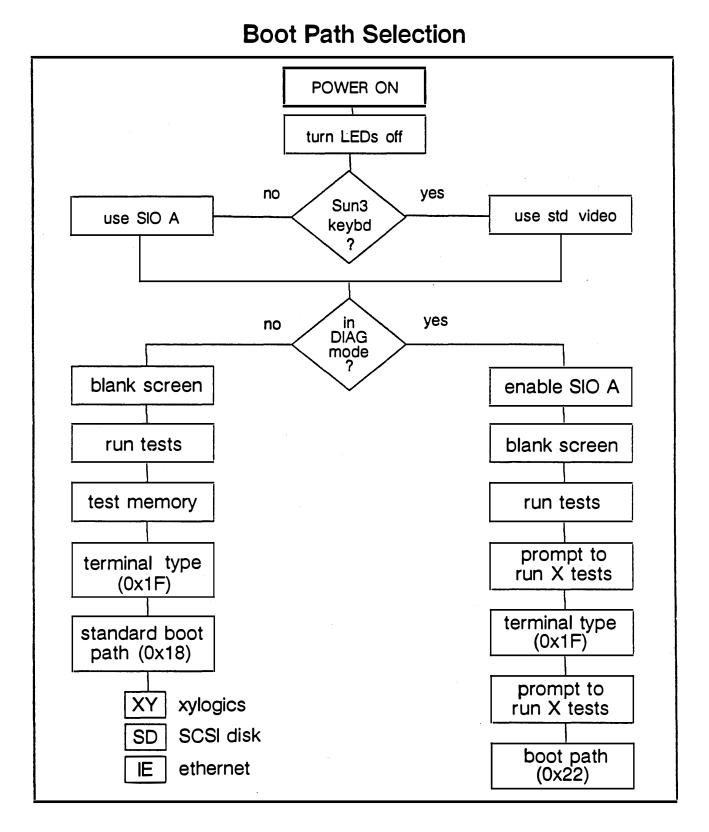

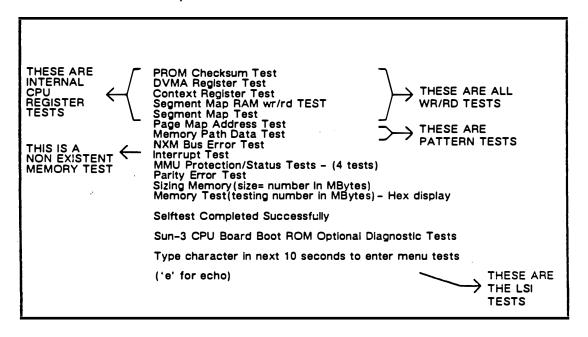

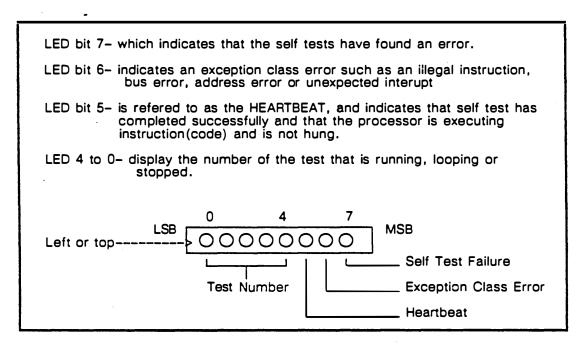

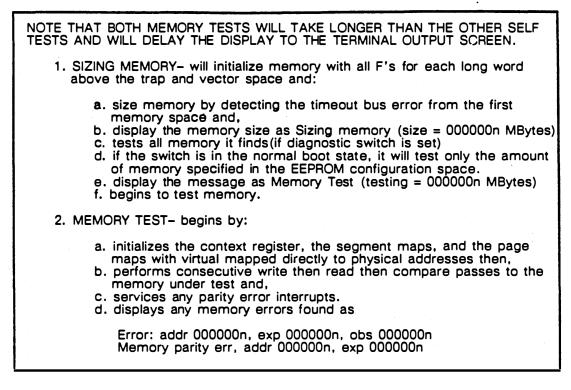

| DEVICE         | DESCRIPTION                                                                                                                                                                                        | DEVIC                                                                          | EVICE SPECIFICATION                                                                                             |                                                                                       |  |